Obsah

1. Architektura mikrořadičů s jádry ARM Cortex-M0 a ARM Cortex-M0+

2. Cortex-M0 a ostatní architektury a čipy ARM

4. Základní vlastnosti mikrořadičů Cortex-M0

7. Odklon od původní čistě RISCové sady A32

8. Thumb versus „klasické“ instrukční sady mikrořadičů

1. Architektura mikrořadičů s jádry ARM Cortex-M0 a ARM Cortex-M0+

Společnost ARM Holdings se v minulosti, tehdy ještě pod dnes již nepožívaným názvem Acorn RISC Machine, proslavila především díky svým 32bitovým RISCovým procesorům ARM, které nabízely vysoký výpočetní výkon a současně i malou spotřebu. Není tedy divu, že tyto čipy byly použity v některých dobových výkonných mikropočítačích, například v počítači Acorn Archimedes a jeho následovnících (Acorn řady R, Acorn řady A apod.). Mezi jednu z největších předností čipů ARM patří i to, že větší a patřičně technologicky vybavené firmy si mohou zakoupit licenci na použití jádra mikroprocesorů ARM ve svých integrovaných obvodech, kde lze (přímo na čipu) zkombinovat vlastní mikroprocesor s dalšími moduly, například s GPU, řadičem sítě (Ethernet, WiFi), řadičem LCD atd. Prakticky stejný způsob licencování společnost ARM používá i u svých mikrořadičů, což jsou ve skutečnosti 32bitová RISCová mikroprocesorová jádra, která lze přímo při návrhu čipů doplnit o další obvody a vytvořit tak mikrořadič vybavený přesně na základě požadavků výrobce, což se vyplácí ve chvíli, kdy je takto navržený čip použit v masově vyráběných zařízeních.

Obrázek 1: Dobový plakát s počítačem Acorn BBC Micro, což byl předchůdce počítače Acorn Archimedes.

V současnosti se můžeme s integrovanými obvody obsahujícími některé jádro mikroprocesoru ARM setkat v nepřeberné řadě různých elektronických zařízení, počínaje (možná poněkud nadneseně řečeno) ovladačem výtahu, přes různě výkonné smartphony, tablety, mikropočítače se SoC typu Raspberry, kapesní herní konzole (pravděpodobně nejznámější je Nintendo 3DS), a konče dnes již poněkud nemódními netbooky či naopak velmi módními zařízeními pro IoT (Internet of Things). U všech těchto elektronických zařízení se ukazuje být velkou předností poměrně malá energetická náročnost mikroprocesorů ARM, a to i v případě serverů, protože s tím, jak cena za hardware obecně postupně klesá, tak současně i celosvětově stoupá cena za elektřinu, která se stává poměrně zásadním faktorem při provozování serverovny či cloudového centa (i když je veřejným tajemstvím, že ve skutečnosti vypadá celý slavný „cloud“ nějak takto :-). Dnes se budeme zabývat popisem architektury těch nejméně výkonných čipů, které jsou dnes v rodině ARM dostupné. Jedná se o mikrořadiče s jádrem Cortex-M0 a Cortex-M0+.

Obrázek 2: Osmibitový mikropočítač Acorn BBC Micro.

2. Cortex-M0 a ostatní architektury a čipy ARM

Mikroprocesory a mikrořadiče ARM za sebou mají dlouhou dobu vývoje, takže není divu, že postupně vznikaly různé generace těchto čipů, které se odlišovaly jak svým výpočetním výkonem, tak i různými změnami v instrukční sadě, uspořádáním cache, počtem řezů (pipeline), použitými submoduly (hardwarová násobička, dělička, jednotka pro SIMD operace) atd. Čipy ARM je možné rozlišit podle architektury, přičemž základní dělení je naznačeno v následující tabulce:

| # | Architektura | Adresová/datová sběrnice | Jádro | Poznámka/profil (u Cortex) |

|---|---|---|---|---|

| 1 | ARMv1 | 26/32 bitů | ARM1 | první implementace, technologické demo |

| 2 | ARMv2 | 26/32 bitů | ARM2, ARM3 | přidána HW násobička a MMU |

| 3 | ARMv3 | 26/32 bitů | ARM6, ARM7 | |

| 4 | ARMv4 | 26/32 bitů | ARM8 | patří sem mj. i řada čipů StrongARM |

| 5 | ARMv5 | 32 bitů | ARM7EJ, ARM9E, ARM10E | lze najít ve starších zařízeních |

| 6 | ARMv6 | 32 bitů | ARM11 | dodnes používaná jádra |

| 7 | ARMv6-M | 32 bitů | Cortex-M0, Cortex-M0+, Cortex-M1 | mikrořadiče (M v názvu) |

| 8 | ARMv7-M | 32 bitů | Cortex-M3 | mikrořadiče (M v názvu) |

| 9 | ARMv7E-M | 32 bitů | Cortex-M4, Cortex-M7 | mikrořadiče (M v názvu) |

| 10 | ARMv7-R | 32 bitů | Cortex-R4, Cortex-R5, Cortex-R7 | realtime aplikace |

| 11 | ARMv7-A | 32 bitů | Cortex-A5, Cortex-A7, Cortex-A8, Cortex-A9, Cortex-A12, Cortex-A15, Cortex-A17 | smartphony atd. |

| 12 | ARMv8-A | 32/64 bitů | Cortex-A53, A57 a A72 | smartphony atd. |

Obrázek 3: Čipy StrongARM založené na architektuře ARMv4 byly v minulosti velmi oblíbené. Zajímavé je, že původně tyto čipy vyvinula společnost Digital Equipment Corporation ve spolupráci s firmou ARM a později byla tato technologie prodána Intelu.

Poznámky:

- U čipů prvních dvou architektur ARMv1 a ARMv2 nebyly použity cache (ani paměťová ani datová), ovšem i samotné CPU byly relativně pomalé (hodinová frekvence 8MHz), takže se tehdy nejednalo o úzké hrdlo systému.

- Můžeme zde vidět dělení na „klasická“ jádra a „Cortex“ jádra.

- V nových elektronických zařízeních se již s prvními čtyřmi generacemi čipů většinou nesetkáme.

- ARM11 je (poněkud zjednodušeně řečeno) poslední doposud masově používané „klasické“ jádro a současně i základ pro velké množství čipů používaných v různých mobilních zařízeních.

- Nové mikroprocesory a mikrořadiče ARM jsou děleny do třech skupin:Application, Realtime, Microcontroller (název první skupiny pravděpodobně vznikl ze snahy o její „napasování“ na zkratku ARM).

- Populární mikropočítač Raspberry používá čip s mikroarchitekturou ARM1176JZF-S, kde prefix ARM1176 značí třetí typ jádra ARM11.

- Právě ARM11 se některými svými vlastnostmi blíží čipům Cortex-M0 a Cortex-M0+, jimiž se dnes budeme zabývat (ARM11 je však určen pro výkonnější aplikace, opět si připomeňme Raspberry a podobná zařízení).

Obrázek 4: Dnes již historický kousek: osobní mikropočítač vybavený mikroprocesorem s architekturou ARM.

3. Produktová řada Cortex-M

Již při letmém pohledu na druhou polovinu tabulky, kterou jsme si ukázali v předchozí kapitole, je patrné, že novější architektury ARM tvoří základ pro jádra třech navzájem odlišných typů čipů. Jedná se o řadu Cortex-M, kde nalezneme jádra určená především pro použití v mikrořadičích (s různým výpočetním výkonem a energetickými nároky), dále pak o řadu Cortex-R určenou pro realtime aplikace (tato jádra jsou mnohdy vybavena instrukcemi typu SIMD) a konečně o řadu Cortex-A, kam patří jak relativně málo výkonné čipy použitelné například v set-top boxech, tak i čipy určené pro servery apod. (tato jádra jsou mnohdy vybavena i matematickým koprocesorem, podporou pro kooperaci většího množství jader, podporou pro adresování až jednoho terabajtu RAM atd.). Pojďme se nyní zaměřit na řadu Cortex-M, tedy na rodinu jader určených pro různě výkonné mikrořadiče:

| # | Jádro | Architektura ARM | Architektura CPU/MCU | MPU |

|---|---|---|---|---|

| 1 | Cortex-M0 | ARMv6-M | Von Neumann | ne |

| 2 | Cortex-M0+ | ARMv6-M | Von Neumann | volitelná |

| 3 | Cortex-M1 | ARMv6-M | Von Neumann | ne |

| 4 | Cortex-M3 | ARMv7-M | Harvardská | volitelná |

| 5 | Cortex-M4 | ARMv7E-M | Harvardská | volitelná |

| 6 | Cortex-M7 | ARMv7E-M | Harvardská | volitelná |

Vidíme, že do řady Cortex-M spadá celkem šest odlišných typů jader, která jsou založena na architektuře ARMv6-M, ARMv7-M či ARMv7E-M. Důležité je si uvědomit, že každá z těchto architektur má odlišné vlastnosti a obecně i jinou instrukční sadu, z čehož také vyplývá, že například mikrořadiče postavené na jádru Cortex-M3 nebudou binárně kompatibilní s mikrořadiči s jádrem Cortex-M0 atd. To však v dnešní době nepředstavuje závažný problém, minimálně ne tak velký, jako je tomu na platformě Wintel.

Poznámka: MPU zde má skutečně význam jednotky pro ochranu vybraných oblastí (regionů) paměti. Nejedná se o jednotku zajišťující virtualizaci paměti (někdy se totiž tyto dvě funkce realizují společně).

Obrázek 5: V oblasti serverů se teprve postupně začínají prosazovat 64bitové čipy ARM.

Podívejme se nyní podrobněji na to, co mají jednotlivá jádra z řady Cortex-M společného a čím se od sebe odlišují. Asi nejdůležitější společnou vlastností je, že Cortex-M nepodporuje původní 32bitovou RISCovou instrukční sady (zde označovanou A32). Namísto toho je podporována instrukční sada Thumb a u některých jader i Thumb-2. Jednodušší jádra nemají hardwarovou děličku ani modul pro DSP operace. Všechny tyto vlastnosti jsou přehledně vypsány v další tabulce:

| # | Jádro | Dělička | DSP | A32 | Thumb | Thumb-2 |

|---|---|---|---|---|---|---|

| 1 | Cortex-M0 | ne | ne | ne | kromě 3 instrukcí | částečně |

| 2 | Cortex-M0+ | ne | ne | ne | kromě 3 instrukcí | částečně |

| 3 | Cortex-M1 | ne | ne | ne | kromě 3 instrukcí | částečně |

| 4 | Cortex-M3 | ano | ne | ne | kompletně | kompletně |

| 5 | Cortex-M4 | ano | ano | ne | kompletně | kompletně |

| 6 | Cortex-M7 | ano | ano | ne | kompletně | kompletně |

Jak je tomu se vzájemnou binární kompatibilitou? Program přeložený pro Cortex-M0 či Cortex-M0+ bude možné provozovat i na vyšších jádrech bez nutnosti jeho modifikace (za předpokladu volby stejného pořadí bajtů – little či big endian). Podobně kód pro Cortex-M3 lze spustit na čipech s jádrem Cortex-M4 či Cortex-M7. Žádný z těchto čipů pochopitelně nedokáže pracovat s kódem používajícím instrukce A32 či s kódem, který používá například rozšíření Neon (SIMD), Jazelle (Java bajtkód), ThumbEE (dtto) atd.

Obrázek 6: Čipy s jádrem ARM nalezneme i v některých herních konzolích.

4. Základní vlastnosti mikrořadičů Cortex-M0

Jádro Cortex-M0 tvoří základ pro čipy, u nichž je žádoucí dosáhnout co nejnižší výrobní ceny, malých rozměrů a malého příkonu (s tím samozřejmě souvisí i příslušně nízký výpočetní výkon). Tato jádra by měla postupně nahrazovat některé aplikace, v nichž se nyní používají osmibitové mikrořadiče. Malé plochy čipu se skutečně podařilo dosáhnout, protože nejmenší vyráběný integrovaný obvod s jádrem Cortex-M0 má plochu přibližně 1,6×2 mm. I spotřeba je velmi nízká, protože dosahuje 12.5µW na každý MHz při použití napětí 1,2V a 64µW na každý MHz při napětí 1,8V (teoreticky roste spotřeba s hodinovou frekvencí lineárně a s napětím kvadraticky, mimochodem hodinová frekvence těchto jader dosahuje podle provedení až několika desítek až stovek MHz, typicky 48 MHz, 80 MHz či 120 MHz). Toto jádro je naprogramované ve Verilogu a po technologické stránce je zajímavé tím, že se interně používá pipeline se třemi řezy, na rozdíl od jádra Cortex-M0+ popsaného v navazujících kapitolách.

Obrázek 7: Čipy XMC4000 založené na jádru Cortex-M0.

Autor původní fotky: Davewave88.

Vzhledem k tomu, že jádra Cortex-M0 jsou používána v aplikacích, kde se požaduje velmi nízký příkon CPU (například různá zařízení s baterií či monočlánkem), podporují tyto čipy hned několik režimů „uspání“ (sleep mode). V základním režimu sleep se jednoduše sníží hodinová frekvence až na 0 Hz, ovšem kromě toho lze použít i režim nazvaný deep sleep, při jehož aktivaci se od napájení odpojí i flash paměť atd. Při práci s různými režimy CPU slouží i instrukce WFI (Wait For Interrupt) a WFE a (Wait for Event). První instrukce čeká na vznik výjimky, přerušení či signálu od debuggeru, druhá instrukce pak na nemaskovanou výjimku, událost přijatou od některého koprocesoru či opět na signál od debuggeru.

Obrázek 8: Jiné zapouzdření čipů XMC4000 založených na jádru Cortex-M0.

Autor původní fotky: Davewave88.

5. Konfigurovatelná násobička

O tom, že jádro Cortex-M0 je skutečně navrženo takovým způsobem, aby mohlo spotřebou energie a částečně i cenou soutěžit s jednoduššími a levnějšími mikrořadiči, svědčí i způsob vyřešení násobičky. V instrukční sadě Thumb nalezneme mj. i instrukci MULS určenou pro násobení dvou 32bitových operandů, přičemž výsledek je taktéž 32bitový (zapamatuje se jen spodních 32bitů výsledku). Při implementaci mikroprocesoru je možné zvolit, jakým typem násobičky se tato instrukce bude provádět. Pokud se má jednat o výkonnější čip (a aplikace násobení skutečně využije), může se použít rychlá násobička, která celou operaci dokáže provést v jediném taktu (samozřejmě se měření provádí při postupně zaplňované pipeline). Pokud se ovšem má jednat o levnější a méně výkonný čip, lze násobení implementovat po krocích (sčítání+bitové posuny), což sice trvá celých 32 taktů, ovšem potřebná plocha čipu a i energetická náročnost je mnohem menší, než v případě jednocyklové násobičky.

Obrázek 9: Mezi další čipy založené na jádru Cortex-M0 patří integrované obvody STM32 F0.

6. Instrukční sada

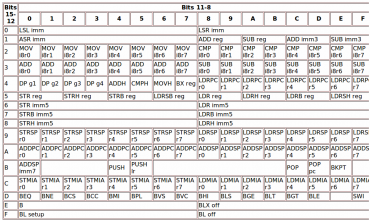

Z předchozího textu již víme, že jádra Cortex-M0 nedokážou správně dekódovat instrukce z původní 32bitové instrukční sady ARM (dnes se označuje jako A32). Namísto toho je podporována instrukční sada Thumb, z níž byly odstraněny jen tři instrukce: CBZ, CBNZ a IT (zejména tato poslední instrukce by však byla velmi užitečná, nicméně její zařazení by asi komplikovalo návrh čipu). Tato jádra navíc rozpoznají i šest instrukcí z instrukční sady Thumb-2, konkrétně se jedná o instrukce BL, DMB, DSB, ISB, MRS a MSR. Důvod, proč se tvůrci přiklonili k instrukční sadě Thumb, je pochopitelný – je tak možné dosáhnout větší hustoty kódu, což je zejména na mikrořadičích, kde jsou kapacity RAM a (Flash)ROM relativně malé, poměrně kritická vlastnost. Díky relativně velké ortogonalitě instrukční sady Thumb se navíc může dosáhnout větší hustoty kódu, než je tomu u některých osmibitových mikrořadičů! (typické je to zejména v porovnání s řadou 51).

Obrázek 10: Kódování instrukcí v sadě Thumb.

7. Odklon od původní čistě RISCové sady A32

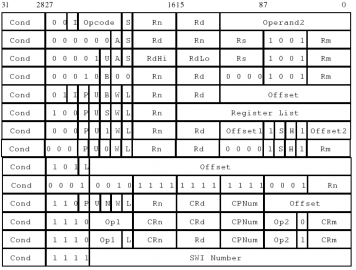

Připomeňme si, že instrukční sada dnes označovaná A32 je založena na původním režimu procesorů ARM, při němž se ideálně v každém taktu načte jedno instrukční slovo o šířce 32 bitů (výjimku tvoří především skoky a taktéž reakce na přerušení). Díky takto širokému instrukčnímu slovu bylo možné instrukční sadu navrhnout tak, aby se v každé instrukci nacházely čtyři podmínkové bity, aby byly aritmetické a logické instrukce tříadresové (tj. obsahovaly adresy dvou zdrojových registrů a registru cílového) a taktéž to, aby se kromě kódu vlastní operace mohl v instrukcích uvést i počet bitů, o něž se má hodnota druhého operandu posunout či zrotovat v barrel shifteru. Tato instrukční sada vycházela z dobových požadavků a zkušeností, kdy se po několika nevydařených projektech se složitými procesory s architekturou CISC konstruktéři obrátili opačným směrem a začali se zabírat procesory s architekturou, pro niž se později vžil název RISC.

Obrázek 11: Kódování instrukcí u „klasické“ 32bitové RISCové architektury.

Ovšem mikroprocesory ARM, které byly původně navrženy pro využití v osobních počítačích, se postupně začaly používat i v jiných oblastech, především ve vestavěných (embedded) systémech, kde vládnou poněkud jiné požadavky. Ve vestavěných systémech je totiž kromě nízké spotřeby, popř. rychlé reakce na přerušení, kladen i velký důraz na to, aby binární obrazy programů byly co nejmenší, protože programy jsou ukládány do pamětí ROM/EPROM/EEPROM/Flash s relativně vysokou cenou za jeden bit a nikoli na vysokokapacitních paměťových médiích (pevné disky) tak, jak je tomu na osobních počítačích. Navíc došlo k postupné změně i v oblasti osobních počítačů – rychlosti procesorů rostly větším tempem, než rychlost pamětí DRAM – což s sebou přinášelo nutnost použití drahých vyrovnávacích pamětí založených na technologii SRAM. V jeden okamžik se dokonce zdálo, že tento vývoj bude znamenat konec procesorů typu RISC, které jsou mj. typické i tím, že používají instrukční sady s instrukcemi pevné šířky (asi nejblíže se klasické architektuře RISC v současnosti blíží mikroprocesory MIPS, kterými jsme se již v tomto seriálu zabývali).

8. Thumb versus „klasické“ instrukční sady mikrořadičů

Odpovědí společnosti ARM na obě nové skutečnosti – požadavek na menší velikost binárních obrazů programů a zvyšující se rozdíl v rychlosti CPU a DRAM – bylo zavedení nové alternativní instrukční sady nazvané Thumb, v níž mají všechny instrukce šířku jen šestnáct bitů, což znamená, že v paměti určité kapacity lze uložit přibližně dvakrát tolik instrukcí Thumb, něž původních RISCových instrukcí (slovo „přibližně“ je zde použito především z toho důvodu, že se v kódu vyskytují i 32bitové konstanty, nezávisle na použité instrukční sadě). Ovšem menší šířka instrukcí znamenala i určitá omezení. Zcela zmizely podmínkové kódy, které zůstaly zachovány jen u instrukce podmíněného skoku. Taktéž se možnost použití barrel shifteru omezila jen na určitou skupinu instrukcí. Ovšem asi největší změnou bylo to, že se sada pracovních registrů R0-R15 rozdělila na spodní polovinu R0-R7 (Lo registers) a horní polovinu R8-R15 (Hi registers), přičemž většina instrukcí dokáže pracovat pouze s prvními osmi registry, zatímco některé registry z horní skupiny mají speciální význam (čítač instrukcí, ukazatel na vrchol zásobníku atd.).

Obrázek 12: Pracovní a řídicí registry: rozdíl mezi RISCovým režimem ARM a režimem Thumb.

Výše zmíněné rozdělení pracovních registrů na dvě poloviny o různých významech je patrné i na těch instrukcích, pomocí nichž se realizují aritmetické a logické operace. Šestnáctibitové instrukční slovo je u těchto instrukcí rozděleno na čtyři části: šestibitový prefix mající binární hodnotu 010000, čtyřbitový kód aritmetické či logické operace, tříbitový index druhého zdrojového registru Rs a taktéž tříbitový index prvního zdrojového registru Rd, který je současně i registrem cílovým, tj. registrem, do nějž se uloží výsledek operace (výjimku tvoří instrukce komparace a testu, u nichž se výsledek porovnání nikam neukládá). Zde je ostatně patrné i další omezení instrukční sady Thumb, kdy do úzkého instrukčního slova není možné vložit indexy tří registrů, ale pouze registrů dvou, což potenciálně zvyšuje četnost přesunů dat mezi registry a navíc se i snižuje účinnost některých optimalizačních technik prováděných buď přímo programátory v assembleru nebo překladači:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+ | 0 | 1 | 0 | 0 | 0 | 0 | operace | Rs | Rd | +---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+

Podporováno je celkem šestnáct aritmetických a logických operací (+ operací bitového posunu a rotace) určených bity 6 až 9 instrukčního slova. Tyto operace jsou vypsány v tabulce pod tímto odstavcem. Ve třetím sloupci tabulky je pro ilustraci uvedena ekvivalentní instrukce dostupná v režimu ARM):

| Kód | Operace | Ekvivalent ARM | Význam |

|---|---|---|---|

| 0000 | AND Rd, Rs | ANDS Rd, Rd, Rs | Rd:= Rd AND Rs |

| 0001 | EOR Rd, Rs | EORS Rd, Rd, Rs | Rd:= Rd EOR Rs (EOR=XOR) |

| 0010 | LSL Rd, Rs | MOVS Rd, Rd, LSL Rs | Rd := Rd << Rs (bitový posun) |

| 0011 | LSR Rd, Rs | MOVS Rd, Rd, LSR Rs | Rd := Rd >> Rs (bitový posun) |

| 0100 | ASR Rd, Rs | MOVS Rd, Rd, ASR Rs | Rd := Rd ASR Rs (aritmetický posun) |

| 0101 | ADC Rd, Rs | ADCS Rd, Rd, Rs | Rd := Rd + Rs + C-bit |

| 0110 | SBC Rd, Rs | SBCS Rd, Rd, Rs | Rd := Rd – Rs – NOT C-bit |

| 0111 | ROR Rd, Rs | MOVS Rd, Rd, ROR Rs | Rd := Rd ROR Rs (rotace) |

| 1000 | TST Rd, Rs | TST Rd, Rs | Nastavení příznaků podle operace Rd AND Rs |

| 1001 | NEG Rd, Rs | RSBS Rd, Rs, #0 | Rd = -Rs |

| 1010 | CMP Rd, Rs | CMP Rd, Rs | Nastavení příznaků podle operace Rd – Rs |

| 1011 | CMN Rd, Rs | CMN Rd, Rs | Nastavení příznaků podle operace Rd + Rs |

| 1100 | ORR Rd, Rs | ORRS Rd, Rd, Rs | Rd := Rd OR Rs |

| 1101 | MUL Rd, Rs | MULS Rd, Rs, Rd | Rd := Rs * Rd |

| 1110 | BIC Rd, Rs | BICS Rd, Rd, Rs | Rd := Rd AND NOT Rs |

| 1111 | MVN Rd, Rs | MVNS Rd, Rs | Rd := NOT Rs |

9. Mikrořadiče Cortex-M0+

Na mikrořadiče Cortex-M0+ se můžeme dívat jako na vylepšení původních jader Cortex-M0. Interně se ovšem jedná o odlišně navržená jádra, protože Cortex-M0+ obsahuje pipeline pouze se dvěma řezy a nikoli s řezy třemi (vlastně se tak vracíme na samotný začátek platformy ARM). Co je však pro případné uživatele důležitější – i díky zmenšenému počtu řezů pipeline se podařilo dále snížit spotřebu a přitom zachovat obousměrnou kompatibilitu s původními jádry Cortex-M0. Spotřeba klesá až na hodnoty 9.8µW na MHz, takže tato jádra mohou nalézt uplatnění i v tak (prozatím) veskrze zbytečných zařízeních, jako jsou chytré hodinky :-) apod. Opět je možné si zvolit způsob implementace násobičky (rychlá versus energeticky nenáročná) a nově i to, zda se má použít jednotka MPU. Čipů s tímto jádrem existuje celá řada, například je vyrábí firmy Atmel, Freescale, STMicroelectronics či NXP Semiconductors.

10. Odkazy na Internetu

- MCU market turns to 32-bits and ARM

http://www.eetimes.com/document.asp?doc_id=1280803 - Cortex-M0 Processor (ARM Holdings)

http://www.arm.com/products/processors/cortex-m/cortex-m0.php - Cortex-M0+ Processor (ARM Holdings)

http://www.arm.com/products/processors/cortex-m/cortex-m0plus.php - ARM Processors in a Mixed Signal World

http://www.eeweb.com/blog/arm/arm-processors-in-a-mixed-signal-world - ARM Architecture (Wikipedia)

https://en.wikipedia.org/wiki/ARM_architecture - Cortex-M0 (Wikipedia)

https://en.wikipedia.org/wiki/ARM_Cortex-M0 - Cortex-M0+ (Wikipedia)

https://en.wikipedia.org/wiki/ARM_Cortex-M#Cortex-M0.2B - Improving ARM Code Density and Performance

New Thumb Extensions to the ARM Architecture Richard Phelan - The ARM Processor Architecture

http://www.arm.com/products/processors/technologies/instruction-set-architectures.php - Thumb-2 instruction set

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0344c/Beiiegaf.html - Introduction to ARM thumb

http://www.eetimes.com/discussion/other/4024632/Introduction-to-ARM-thumb - ARM, Thumb, and ThumbEE instruction sets

http://www.keil.com/support/man/docs/armasm/armasm_CEGBEIJB.htm - An Introduction to ARM Assembly Language

http://dev.emcelettronica.com/introduction-to-arm-assembly-language - Processors – ARM

http://www.arm.com/products/processors/index.php - The ARM Instruction Set

http://simplemachines.it/doc/arm_inst.pdf