Obsah

1. Mikroprocesory a mikrořadiče s jádrem SH-2A aneb vítězství superskalární architektury

2. Základní vlastnosti čipů SH-2A

3. Harvardská architektura a externí sběrnice

5. Rozšíření možností při načítání konstant

6. Instrukce určené pro provádění bitových operací

7. Uložení či načtení většího množství registrů

8. Oříznutí příliš velkých či malých hodnot při zpracování signálu instrukcí CLIPx

9. Nové instrukce pro násobení a dělení

10. Přídavné instrukce pro práci se stavovým bitem T

11. Použití dvanáctibitového offsetu při adresování dat v operační paměti

1. Mikroprocesory a mikrořadiče s jádrem SH-2A aneb vítězství superskalární architektury

Čipy s původní instrukční sadou SH-2, kterou jsme si popsali v předchozích dvou článcích, se sice doposud používají, ale většinou se již setkáme buď s instrukční sadou SH-4 (tou se budeme zabývat příště) nebo s instrukční sadou SH-2A. Mikroprocesory a mikrořadiče SH-2A jsou při použití shodné hodinové frekvence obecně mnohem výkonnější, než původní jádra SH-2. Větší výpočetní rychlost SH-2A je způsobena více faktory; nejdůležitější je však to, že v čipech SH-2A je použita superskalární architektura, takže je možné (samozřejmě v ideálním případě, tj. pokud nedojde ke konfliktům) v jednom taktu dokončit dvě instrukce. Superskalární architektura je dále podporována použitím Harvardského procesoru, kdy je datová sběrnice oddělena od sběrnice použité pro načítání instrukcí (tím se výrazně sníží počet kolizí při přístupu do operační paměti). Navíc je instrukční sada SH-2A doplněna o řadu nových instrukcí, s nimiž se seznámíme v navazujících kapitolách.

2. Základní vlastnosti čipů SH-2A

Čipy SH-2A byly navrženy zejména s ohledem na jejich praktické použití v mikrořadičích a při zpracování signálů. Můžeme zde vidět určitý odklon od čisté RISCové architektury, který je zejména patrný u instrukcí s 32bitovým instrukčním slovem, protože původní instrukce měly konstantní šířku šestnácti bitů (to sice pravděpodobně způsobilo nějaké komplikace v dekodéru instrukcí, ovšem na druhou stranu to vedlo ke zvýšení efektivity kódu). Dále byly přidány takzvané banky registrů, s jejichž využitím bylo možné zrychlit vstup a zahájení běhu přerušovací rutiny na šest cyklů. Přidány byly instrukce určené pro zjednodušení zpracování signálů (clipping), dále pak instrukce pro implementaci Booleovského procesoru (operace s jednotlivými bity), blokové přenosy registrů atd. Volitelně bylo možné čip rozšířit i o matematický koprocesor s vlastní sadou pracovních registrů a instrukcí.

3. Harvardská architektura a externí sběrnice

Původní pipeline s pěti řezy, o níž jsme se zmínili při popisu čipů SH-2, je v případě čipů SH-2A rozšířena takovým způsobem, aby bylo možné zpracovávat současně dvě instrukce. Uvnitř čipů nalezneme dvojici sběrnic pojmenovaných F-bus a M-bus, přičemž první sběrnice slouží pouze pro načítání instrukcí (zápis do paměti instrukcí se neprovádí, u mikrořadičů je to ještě zvýrazněno použitím Flash EEPROM namísto běžné DRAM) a druhá sběrnice slouží pro přenos dat. Díky tomuto poměrně striktnímu oddělení instrukcí od dat bylo možné dosáhnout toho, aby se poslední fáze zpracování instrukce v pipeline (WB – write back) popř. prostřední fáze (MA – memory access) mohla překrývat s první fází jiné instrukce (IF – instruction fetch), a to bez vzniku konfliktu. Toto rozdělení je dále podpořeno i rozdělením cache první úrovně, která má pro instrukce kapacitu 8 kB a pro data taktéž 8 kB.

4. Banky pracovních registrů

Zejména pro rychlé reakce na přerušení (spuštění algoritmu v přerušovací rutině) jsou procesory SH-2A vybaveny takzvanými bankami registrů. V každém banku je uloženo devatenáct 32bitových registrů – patnáct pracovních registrů R0 až R14 (bez R15), řídicí registr GBR, registry MACH a MACL popsané minule (viz operaci multiply and accumulate) a registr PR. Celkově je k dispozici patnáct banků, mezi nimiž je možné se přepínat. Přepnutím je zde myšlena operace, při níž se naplní všech devatenáct zmíněných registrů hodnotami z vybraného banku. Mezi aktuálním bankem a jiným bankem lze přenášet vždy obsah jednoho registru instrukcemi LDBANK a STBANK, viz též následující tabulka instrukcí (zdrojovým a cílovým registrem v aktuálním banku je vždy R0):

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | RESBANK | 9 | přepnutí banky registrů a tím pádem přepsání všech 19 výše zmíněných registrů |

| 2 | STBANK | 7 | uložení registru R0 do vybrané banky registrů |

| 3 | LDBANK | 6 | načtení registru R0 z vybrané banky registrů |

5. Rozšíření možností při načítání konstant

Mnoho typů RISCových procesorů, včetně původních čipů s instrukční sadou SH-2, trpí jedním společným nedostatkem – kvůli použití instrukcí pevné délky, která většinou odpovídá bitové šířce zpracovávaných operandů (typicky 32 bitů) není možné, aby v instrukční sadě existovala instrukce, která dokáže načíst celou 32bitovou konstantu. U původních procesorů SH-2 byla situace ještě o něco horší, protože kvůli 16bitovým slovům byla ve skutečnosti šířka konstant omezena na pouhých osm bitů. Typickým příkladem je instrukce MOV #imm, Rn (nejdříve se zapisuje zdrojový operand, poté operand cílový) s formátem:

15 12 8 4 0 +----+----+----+----+ |1110|dddd|iiii iiii| +----+----+----+----+

Toto poměrně zásadní omezení bylo u instrukční sady SH-2A odstraněno, protože několik vybraných instrukcí má šířku 32 bitů. To ve skutečnosti nepřináší velká omezení, protože šířka externí sběrnice pro načítání instrukcí je 32bitová, takže se „pouze“ zmenší datový tok u několika instrukcí. U dvou nových instrukcí pojmenovaných MOVI20 a MOVI20S je použita 20bitová hodnota, která je při načítání instrukčního slova znaménkově rozšířena, tj. v praxi lze pracovat s hodnotami od –219 do 219-1. Povšimněte si, že obě nové instrukce trvají pouhý jeden takt:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MOVI20 | 1 | přenos konstanty o šířce 20 bitů do registru Rn |

| 2 | MOVI20S | 1 | dtto, ale konstanta je posunuta o osm bitů doleva |

Formát instrukce MOVI20 vypadá takto (dddd je index registru Rn a iiii první čtyři bity konstanty):

15 12 8 4 0 15 12 8 4 0 +----+----+----+----+ +----+----+----+----+ |0000|dddd|iiii|0000| |spodních 16 bitů # | +----+----+----+----+ +----+----+----+----+

Formát instrukce MOVI20S je prakticky stejný, až na nejnižší bit prvního instrukčního slova:

15 12 8 4 0 15 12 8 4 0 +----+----+----+----+ +----+----+----+----+ |0000|dddd|iiii|0001| |spodních 16 bitů # | +----+----+----+----+ +----+----+----+----+

V praxi se tedy můžeme setkat s následujícími způsoby načtení konstanty. U osmibitové konstanty se použije obyčejná instrukce MOV, u konstanty 20bitové instrukce MOVI20, u konstanty s šířkou do 28 bitů můžeme použít kombinaci MOVI20S+OR a konečně pokud je konstanta širší, nezbývá nic jiného, než ji uložit někam za aktuální subrutinu a načíst ji adresováním přes hodnotu registru PC+offset (výběr samozřejmě v případě vyššího programovacího jazyka provádí překladač):

| Konstanta | Sekvence instrukcí |

|---|---|

| 8 bitů | MOV #konstanta, R0 |

| 16 bitů | MOVI20 #konstanta, R0 |

| 20 bitů | MOVI20 #konstanta, R0 |

| 28 bitů | MOVI20S #konstanta, R0 OR #k8, R0 |

| 32 bitů | MOV @(offset, PC), R0 |

6. Instrukce určené pro provádění bitových operací

V oblasti mikrořadičů se již od dob slavného (a bohužel dodnes používaného) čipu Intel 8051 (MCS-51) můžeme setkat s implementací takzvaného Booleovského procesoru. Tímto poněkud nadneseným jménem se označuje sada instrukcí, které dokážou pracovat na úrovni jednotlivých bitů a nikoli celých slov, a to (většinou) dokonce takovým způsobem, že i přístup do paměti či do řídicích registrů periferních zařízení je prováděn po jednom bitu (například negace jediného bitu je rozdílná operace od přečtení bajtu/slova do akumulátoru, negace vybraného bitu a zápis celého bajtu/slova zpět). Jen pro zajímavost: na již zmíněném mikrořadiči MCS-51 je implementován úplný Booleovský procesor s jednobitovým akumulátorem (tím je příznak C/carry), 128 bitovou oblastí RAM a 128 bitovou oblastí speciálních řídicích registrů (SFR).

Tento původní Booleovský procesor měl k dispozici devět instrukcí. S podobným konceptem jsme se seznámili i při popisu jader Cortex-M3 a nalezneme ho i u čipů s instrukční sadou SH-2A, kde je k dispozici čtrnáct nových instrukcí. Ty lze rozdělit do čtyř skupin. V první skupině nalezneme instrukce pro vynulování či nastavení vybraného bitu pracovního registru. Tyto instrukce trvají jeden takt. Ve druhé skupině jsou instrukce, které vybraný bit pracovního registru přenesou do příznakového bitu T či naopak. I tyto instrukce trvají jeden takt. Třetí skupinu tvoří instrukce pro nastavení či vynulování bitu v paměti; zde si již ovšem počkáme tři takty. A konečně v poslední skupině jsou instrukce, které zkombinují příznakový bit T s bitem načteným z operační paměti. I tyto instrukce trvají tři takty:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | BCLR | 1 | vynulování i-tého bitu registru Rn |

| 2 | BSET | 1 | nastavení i-tého bitu registru Rn (na 1) |

| 3 | BLD | 1 | přenos i-tého bitu registru Rn do příznakového bitu T |

| 4 | BST | 1 | přenos příznakového bitu T do i-tého bitu registru Rn |

| 5 | BCLR.B | 3 | uložení 0 na i-tý bit na adrese (disp + Rn)) |

| 6 | BSET.B | 3 | uložení 1 na i-tý bit na adrese (disp + Rn)) |

| 7 | BLD.B | 3 | načtení i-tého bitu z adresy (disp + Rn) a uložení do T |

| 8 | BLDNOT.B | 3 | negace předchozího výpočtu |

| 9 | BST.B | 3 | uložení T do i-tého bitu na adrese (disp + Rn) |

| 10 | BAND.B | 3 | (i-tý bit z adresy (disp + Rn)) ∧ T → T |

| 11 | BANDNOT.B | 3 | negace předchozího výpočtu |

| 12 | BOR.B | 3 | (i-tý bit z adresy (disp + Rn)) | T → T |

| 13 | BORNOT.B | 3 | negace předchozího výpočtu |

| 14 | BXOR.B | 3 | (i-tý bit z adresy (disp + Rn)) ⊕ T → T |

7. Uložení či načtení většího množství registrů

Zajímavé a přitom užitečné je, že i u mikroprocesorů a mikrořadičů s instrukční sadou SH-2A došlo k přidání instrukcí sloužících pro načtení většího množství registrů z operační paměti či naopak pro uložení většího množství registrů zpět do operační paměti. Podobné instrukce nalezneme například i u mikroprocesorů ARM s instrukcemi LDM a STM (viz též [1]). V instrukční sadě SH-2A sice nemáme možnost si zvolit registry pomocí bitové masky, ale určitá volba zde přece jen existuje – můžeme zvolit rozsah indexů ukládaných či načítaných registrů od 0 do R14 (poslední registr R15 je použit pro adresování). Podívejme se na čtveřici nových instrukcí, která se pro tyto účely používá:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MOVML.L Rm,@-R15 | 1 až 16 | zápis registrů R0..Rm do paměti adresované R15 |

| 2 | MOVML.L @R15+,Rn | 1 až 16 | přečtení registrů R0..Rn z paměti adresované R15 |

| 3 | MOVMU.L Rm,@-R15 | 1 až 16 | zápis PR a registrů Rn..R14 do paměti adresované R15 |

| 4 | MOVMU.L @R15+,Rn | 1 až 16 | přečtení registrů PR a Rn..R14 z paměti adresované R15 |

Povšimněte si, že doba trvání těchto instrukcí je proměnná a pochopitelně závisí na počtu ukládaných či načítaných registrů.

8. Oříznutí příliš velkých či malých hodnot při zpracování signálu instrukcí CLIPx

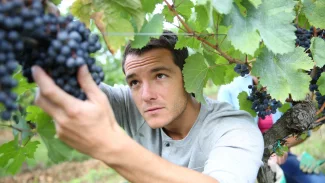

Instrukce popsané v této kapitole jsou velmi užitečné při zpracování signálů. Pro ilustraci si představme zpracování obrázků s osmibitovými hodnotami pixelů:

Obrázek 1: Zdrojový rastrový obrázek (známá fotografie Lenny), který tvoří zdroj pro jednoduchý konvoluční (FIR) filtr, jenž zvyšuje hodnoty pixelů o pevně zadanou konstantu (offset).

Obrázek 2: Pokud je pro přičtení offsetu použita operace součtu se zanedbáním přenosu (carry), tj. když se počítá systémem „modulo N“, dochází při překročení maximální hodnoty pixelu (čistě bílá barva) k jasně viditelným chybám.

Obrázek 3: Při použití operace součtu se saturací sice taktéž dojde ke ztrátě informace (vzniknou oblasti s pixely majícími hodnotu 255), ovšem viditelná chyba je mnohem menší, než na předchozím obrázku.

Aby nebylo nutné po každém sčítání, násobení atd. neustále kontrolovat, zda došlo k přetečení, byla u některých typů procesorů zavedena takzvaná aritmetika se saturací, což zjednodušeně řečeno znamená, že při provádění vybraných aritmetických operací nikdy nedošlo k přetečení či podtečení. U mikroprocesorů s instrukční sadou SH-2A je tomu jinak, protože aritmetické operace zůstaly nezměněny (ani se nijak nerozšířily), ovšem ihned po jejich provedení lze aplikovat jednu z vybraných ořezových operací (pro bajty či 16bitová slova, navíc buď pro hodnoty se znaménkem či bez znaménka):

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | CLIPS.B Rn | 1 | když Rn > 127, zapiš do Rn 127 a nastav CS totéž pro podmínku Rn < –128 |

| 2 | CLIPS.W Rn | 1 | když Rn > 32767, zapiš do Rn 32767 a nastav CS totéž pro podmínku Rn < –32768 |

| 3 | CLIPU.B Rn | 1 | když Rn > 255, zapiš do Rn 255 a nastav CS |

| 4 | CLIPU.W Rn | 1 | když Rn > 65535, zapiš do Rn 65535 a nastav CS |

Poznámka: CS je označení bitu uloženého ve stavovém registru SR.

9. Nové instrukce pro násobení a dělení

Připomeňme si, že mikroprocesory s instrukční sadou SH-2 vlastně nepodporovaly instrukci pro provedení celočíselného dělení, ať již čísel se znaménkem nebo bez znaménka. Namísto toho se používaly tři instrukce nazvané DIV0S, DIV0U a DIV1. První dvě instrukce připravily stavové bity M, Q a T používané při dělení a třetí instrukce vždy provedla jeden krok dělení. Taktéž násobení bylo omezeno, protože výsledek se ukládal do registru MAC, nikoli do běžného pracovního registru. S tímto omezením se již na čipech SH-2A nesetkáme, a to díky trojici nových instrukcí popsaných v následující tabulce:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MULR | 2 | operace Rn × R0 → Rn |

| 2 | DIVU | 36 | operace Rn ÷ R0 → Rn (hodnoty bez znaménka) |

| 3 | DIVS | 34 | operace Rn ÷ R0 → Rn (hodnoty se znaménkem) |

Poznámka: pozorněji si u posledních dvou řádků prohlédněte sloupec nadepsaný „Počet cyklů“, aby byl jasně patrný rozdíl mezi již popsanými instrukcemi DIV0S, DIV0U a DIV1, které sice trvají pouhý jeden takt, ovšem provedou vždy jen jeden krok dělení (někdy není nutné skutečně dělit celá 32bitová čísla, proto mají tyto instrukce svůj význam).

10. Přídavné instrukce pro práci se stavovým bitem T

Tato kapitola bude v porovnání s ostatními kapitolami velmi krátká, protože si v ní popíšeme pouze dvě nové instrukce, které slouží pro operace se stavovým bitem T (Test). Připomeňme si, že pro přímou manipulaci s tímto bitem existuje už v původních procesorech s instrukční sadou SH-2 trojice instrukcí nazvaných MOVT, CLRT a SETT, viz též následující tabulku:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MOVT | 1 | uložení bitu T do zvoleného registru Rn (nastaví se nejnižší bit registru, ostatní bity se vynulují) |

| 2 | CLRT | 1 | vynulování stavového bitu; 0→T |

| 3 | SETT | 1 | nastavení stavového bitu; 1→T |

K těmto třem instrukcím byly přidány další dvě instrukce, z nichž jedna přenáší negovanou hodnotu stavového bitu T do zvoleného registru Rn a druhá instrukce tento bit neguje. Obě tyto nové instrukce jsou podle očekávání dokončeny v jediném taktu:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MOVRT | 1 | přenos negovaného bitu T do vybraného registru Rn |

| 2 | NOTT | 1 | negace stavového bitu; T=~T |

11. Použití dvanáctibitového offsetu při adresování dat v operační paměti

Při popisu nových instrukcí MOVI20 a MOVI20S jsme se seznámili s konceptem použití dvojnásobné šířky instrukčního slova, tj. s využitím 32bitového slova namísto slova šestnáctibitového. Podobným způsobem byly rozšířeny i instrukce přenášející data mezi vybraným pracovním registrem a operační pamětí adresovanou s využitím offsetu přičteného k jinému pracovnímu registru. Rozšířené instrukce dokážou pracovat s dvanáctibitovým offsetem, což samozřejmě rozšiřuje možnosti při použití velkých datových struktur atd. Podívejme se, o jaké instrukce se jedná:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | MOV.B Rm,@(disp12,Rn) | 1 | zápis bajtu z registru Rm na adresu (disp12+Rn) |

| 2 | MOV.W Rm,@(disp12,Rn) | 1 | zápis 16bitového slova z registru Rm na adresu (disp12+Rn) |

| 3 | MOV.L Rm,@(disp12,Rn) | 1 | zápis 32bitového slova z registru Rm na adresu (disp12+Rn) |

| 4 | MOV.B @(disp12,Rm),Rn | 1 | čtení bajtu z adresy (disp12+Rm) o registru Rn |

| 5 | MOV.W @(disp12,Rm),Rn | 1 | čtení 16bitového slova z adresy (disp12+Rm) o registru Rn |

| 6 | MOV.L @(disp12,Rm),Rn | 1 | čtení 32bitového slova z adresy (disp12+Rm) o registru Rn |

Formát všech těchto instrukcí je totožný:

15 12 8 4 0 15 12 8 4 0 +----+----+----+----+ +----+----+----+----+ |0011|dddd|ssss|0001| |kód | displacement | +----+----+----+----+ +----+----+----+----+

Kde:

- ssss je index zdrojového pracovního registru (source)

- dddd je index cílového pracovního registru (destination)

- kód vybírá konkrétní instrukci

- displacement je dvanáctibitový offset

12. Další nové instrukce

Mezi další instrukce, které najdeme pouze na čipech SH-2A a nikoli na čipech SH-2, patří zejména tyto instrukce:

| # | Zkratka | Počet cyklů | Stručný popis instrukce |

|---|---|---|---|

| 1 | SHAD | 1 | aritmetický posun doleva či doprava podle obsahu pracovního registru |

| 2 | SHLD | 1 | bitový posun doleva či doprava podle obsahu pracovního registru |

| 3 | JSR/N | 5 | skok do subrutiny (ovšem bez branch delay slotu) |

| 4 | RTS/N | 3 | návrat ze subrutiny (opět bez branch delay slotu) |

| 5 | RTV/N | 3 | uložení vybraného registru do R0 a návrat ze subrutiny (opět bez branch delay slotu) |

| 6 | PREF | 1 | cache prefetch |

13. Jádro SH2A-FPU

Některé čipy s instrukční sadou SH-2A mohou být doplněny o matematický koprocesor, který je ovládán doplňkovou sadou instrukcí označovaných názvem SH2A-FPU a taktéž má k dispozici vlastní skupinu pracovních registrů. Většina těchto instrukcí, které si podrobněji popíšeme příště, je dokončena v jediném taktu, výjimkou jsou pouze instrukce pro konverzi operandů (dva takty), některé operace s čísly s dvojnásobnou přesností (součet v šesti taktech) a zejména pak instrukce podílu, která je pro hodnoty s jednoduchou přesností dokončena v deseti cyklech a pro hodnoty s dvojnásobnou přesností až v 23 cyklech (zajímavé je, že výpočet druhé odmocniny je se šesti resp. 22 cykly nepatrně rychlejší).

14. Odkazy na Internetu

- SH7201 Group User's Manual: Hardware

https://www.renesas.com/en-us/document/hw-manual?hwLayerShowFlg=true&prdLayerId=2038&layerName=SH7201&coronrService=document-prd-search&hwDocUrl=%2Fen-us%2Fdoc%2Fproducts%2Fmpumcu%2Fdoc%2Fsuperh%2Fr01uh0026ej_sh7201_hm.pdf&hashKey=4d1ed116961466babf99bc7cf1d2cdec - SH7203 Group User's Manual: Hardware

https://www.renesas.com/en-us/document/hw-manual?hwLayerShowFlg=true&prdLayerId=2126&layerName=SH7203&coronrService=document-prd-search&hwDocUrl=%2Fen-us%2Fdoc%2Fproducts%2Fmpumcu%2F001%2Fr01uh0458ej0400_sh7203.pdf&hashKey=68baf3ad6c52e9e2616e44024589e8cf - SuperH RISC engine Family Features

https://www.renesas.com/en-us/products/microcontrollers-microprocessors/superh/superh-features.html - Konkurence procesorů s mikroprogramovým řadičem – RISC

http://www.root.cz/clanky/konkurence-procesoru-s-mikroprogramovym-radicem-architektura-risc/ - Mikroprocesory s architekturou RISC I

http://www.root.cz/clanky/mikroprocesory-s-architekturou-risc-i/ - Procesory RISC v pracovních stanicích a serverech

http://www.root.cz/clanky/procesory-s-architekturou-risc-v-pracovnich-stanicich-a-serverech/ - Procesory RISC v pracovních stanicích a serverech – architektura SPARC V8 a

http://www.root.cz/clanky/procesory-risc-v-pracovnich-stanicich-a-serverech-architektura-sparc-v8-a-v9/ - Procesory RISC v pracovních stanicích a serverech – architektura PA-RISC

http://www.root.cz/clanky/procesory-risc-v-pracovnich-stanicich-a-serverech-architektura-pa-risc/ - Rozšíření instrukční sady procesorových jader s otevřenou architekturou RISC-V

http://www.root.cz/clanky/rozsireni-instrukcni-sady-procesorovych-jader-s-otevrenou-architekturou-risc-v/ - Sega documentation

http://koti.kapsi.fi/~antime/sega/docs.html - 1995 Programming on the Sega Saturn

http://cowboyprogramming.com/2010/06/03/1995-programming-on-the-sega-saturn/ - Sega Myths-Saturn was the most difficult console to program for of 5th Gen

http://forums.sega.com/showthread.php?313485-Sega-Myths-Saturn-was-the-most-difficult-console-to-program-for-of-5th-Gen - SuperH RISC engine Family

http://www.renesas.com/products/mpumcu/superh/index.jsp - Sega Saturn

http://en.wikipedia.org/wiki/Sega_saturn - Fourth-Generation Consoles

http://gaming.wikia.com/wiki/Fourth-Generation_Consoles - Fifth-Generation Consoles

http://gaming.wikia.com/wiki/Fifth-Generation_Consoles - History of video game consoles (fifth generation)

http://en.wikipedia.org/wiki/History_of_video_game_consoles_(fifth_generation) - Sega Mega Drive

http://sega.jp/archive/segahard/md/ - Sega Archives

http://sega.jp/archive/segahard/ - Sega Genesis

http://www.dmoz.org/Games/Video_Games/Console_Platforms/Sega/Genesis/ - The Sega Mega Drive/Genesis

http://www.captainwilliams.co.uk/sega/megadrive/megadrive.php - Sega Master System Museum

http://alexkidd.com/ - Jadeite's Sega Master System Museum

http://rp_gamer.tripod.com/SMS/1.html - Sega Master System (Wikipedia)

http://en.wikipedia.org/wiki/Sega_Master_System - Sega Card (Wikipedia)

http://en.wikipedia.org/wiki/Sega_Card - Sega Master System VDP documentation

http://www.smspower.org/uploads/Development/msvdp-20021112.txt?sid=28c370e1fcac51d5774319979bf96f4c - The16bit Era Of Console Video Games

http://tvtropes.org/pmwiki/pmwiki.php/Main/The16bitEraOfConsoleVideoGames - The Console Wars

http://www.cracked.com/funny-2590-the-console-wars/ - Console Wars

http://tvtropes.org/pmwiki/pmwiki.php/Main/ConsoleWars - Era of the „Bit Wars“

http://www.gtplanet.net/forum/threads/era-of-the-bit-wars.119796/ - Rez Wars: How the Bit Wars never really ended

http://www.ign.com/blogs/beastmastertoad/2013/01/31/rez-wars-how-the-bit-wars-never-really-ended - Which system ended the „Bit Wars“?

http://atariage.com/forums/topic/199163-which-system-ended-the-bit-wars/ - Status Register

https://en.wikipedia.org/wiki/Status_register - Introduction to ARM Thumb

http://www.embedded.com/electronics-blogs/beginner-s-corner/4024632/Introduction-to-ARM-thumb - Code Size – a comprehensive comparison of microMIPS32 and Thumb code size using many Megabytes of customer code

https://community.arm.com/groups/processors/blog/2014/04/28/code-size-a-comprehensive-comparison-of-micromips32-and-thumb-code-size-using-many-megabytes-of-customer-code - MIPS MCUs Outrun ARM

http://www.linleygroup.com/newsletters/newsletter_detail.php?num=5117 - Carry bits, The Architect's Trap

http://yarchive.net/comp/carry_bit.html - Microprocessor Design/ALU Flags

https://en.wikibooks.org/wiki/Microprocessor_Design/ALU_Flags - Flags register in an out-of-order processor

http://cs.stackexchange.com/questions/42095/flags-register-in-an-out-of-order-processor - Berkeley RISC

http://en.wikipedia.org/wiki/Berkeley_RISC - Great moments in microprocessor history

http://www.ibm.com/developerworks/library/pa-microhist.html - RISC vs. CISC

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/risccisc/ - RISC and CISC definitions:

http://www.cpushack.com/CPU/cpuAppendA.html - The Evolution of RISC

http://www.ibm.com/developerworks/library/pa-microhist.html#sidebar1