Obsah

1. RISCové mikroprocesory AMD 29000

2. Základní informace o mikroprocesorech AMD 29000

3. Procesory AMD 29000 s trojicí externích sběrnic

4. Globální a lokální registry

6. Formát instrukcí procesorů AMD 29000

7. Instrukční soubor procesorů AMD 29000

8. Od čipů AMD 29000 k mikroprocesorům AMD K5 a AMD K6

1. RISCové mikroprocesory AMD 29000

V předchozích dvou částech seriálu o architekturách počítačů jsme si popsali princip činnosti zásobníkových mikroprocesorů a zmínili jsme se i o některých zajímavých čipech s touto architekturou (WISC CPU/16, Harris RTX 2000, F21, c18, b16 …). V části dnešní se však již vrátíme zpět k původnímu tématu – k mikroprocesorům s architekturou RISC. Pouze pro úplnost připomenu, že jsme se již zabývali popisem čipů RISC I, RISC II, MIPS, SPARC a PA-RISC; ovšem mikroprocesorů s architekturou RISC je ve skutečnosti mnohem více. Jedním z těchto mikroprocesorů je i 32bitový čip nazvaný AMD 29000. Společnost AMD tento čip nabízela jako následovníka procesoru AMD 2900 složeného z bitových řezů, jehož popisem jsme se již taktéž v tomto seriálu zabývali. I přes podobné typové označení AMD 2900 vs. AMD 29000 se však z technologického hlediska i z pohledu programátora jedná o naprosto rozdílné mikroprocesory.

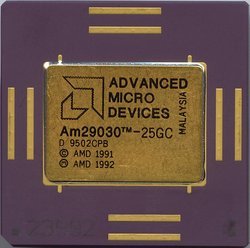

Obrázek 1: Integrovaný obvod AMD Am2901 tvořící ústřední část modulární architektury AMD Am2900. Zde zobrazený čip pochází z řady určené mj. i pro armádní účely (jeho charakteristiky tedy umožňují práci ve větším teplotním rozsahu atd.).

První varianty mikroprocesoru AMD 29000 (nazývaného též AMD 29k nebo jen 29k) se na trhu objevily v roce 1988, tj. relativně pozdě v porovnání například s čipy MIPS a dokonce o rok později než mikroprocesory SPARC. Jednalo se ovšem o populární čipy; společnost AMD i někteří publicisté dokonce v jeden okamžik používali slogan „the most popular RISC processor“. Původní typ AMD 29000 obsahoval na jednom čipu jak mikroprocesor, tak i jednotku pro práci s pamětí (MMU), ovšem nikoli již matematický koprocesor, který byl nabízen jako samostatný integrovaný obvod. Později došlo k zařazení matematického koprocesoru k vlastnímu mikroprocesoru: jednalo se o čipy AMD 29040 a AMD 29050 (tabulka s různými typy čipů patřících do této rodiny je uvedena ve druhé kapitole). Ovšem i přes oblibu řady 29k byl již v roce 1995 další vývoj těchto procesorů zastaven, protože se firma AMD začala více soustředit na vývoj vlastních verzí procesorů s architekturou x86, jejichž výroba byla více rentabilní.

Obrázek 2: Klon výše zobrazeného čipu AMD Am2901, který pochází ze SSSR.

2. Základní informace o mikroprocesorech AMD 29000

Mikroprocesory řady AMD 29000 mají mnoho vlastností společných s dalšími mikroprocesory s architekturou RISC, které jsme si již v tomto seriálu popsali. Jedná se například o použití velkého množství pracovních registrů rozdělených na registry globální a registry lokální dostupné přes registrové okno, dále pak o využití instrukční pipeline, která je v případě řady AMD 29000 složena ze čtyř řezů. Podobný je i instrukční soubor obsahující takzvané tříadresové instrukce, tj. instrukce obsahující dva zdrojové operandy a jeden operand cílový. Ovšem některými dalšími vlastnostmi se procesory AMD 29000 od svých protějšků odlišují, například použitím registrových oken s proměnnou velikostí a taktéž Harvardskou architekturou, kterou některé čipy AMD 29000 využívají. Použití Harvardské architektury vychází z toho, že některé mikroprocesory z rodiny AMD 29000 byly navrženy i pro instalace ve vestavných zařízeních, tj. nikoli v univerzálních počítačích s jediným typem paměti.

Obrázek 3: Integrovaný obvod Am2901.

V rámci rodiny AMD 29000 vzniklo poměrně velké množství mikroprocesorů různých vlastností i dalších podpůrných čipů, včetně mikrořadičů. Některé z těchto čipů jsou vypsány v následující tabulce:

| Označení čipu | Frekvence | Stručný popis |

|---|---|---|

| Am29000 | 16, 20, 25, 33 | RISCový mikroprocesor se třemi sběrnicemi, základ celé rodiny 29k |

| Am29005 | 16 | procesor pinově kompatibilní s Am29000, bez cache, nabízí menší výpočetní výkon i cenu |

| Am29050 | 20, 25, 33, 40 | procesor pinově kompatibilní s Am29000 + matematický koprocesor, vyšší výpočetní výkon i cena |

| Am29030 | 20, 25, 33 | RISCový mikroprocesor s dvojicí sběrnic |

| Am29035 | 16 | procesor pinově kompatibilní s Am29030, menší cache |

| Am29040 | 33, 40, 50 | procesor pinově kompatibilní s Am29030, vyšší frekvence |

| Am29200 | 16, 20 | mikrořadič, tj. procesor + paměti na jednom čipu |

| Am29205 | 12, 16 | mikrořadič, levnější než Am29200, pouzdro s méně piny |

Obrázek 4: Zjednodušený blokový diagram čipu Am2901.

Zdroj: technické materiály firmy AMD.

3. Procesory AMD 29000 s trojicí externích sběrnic

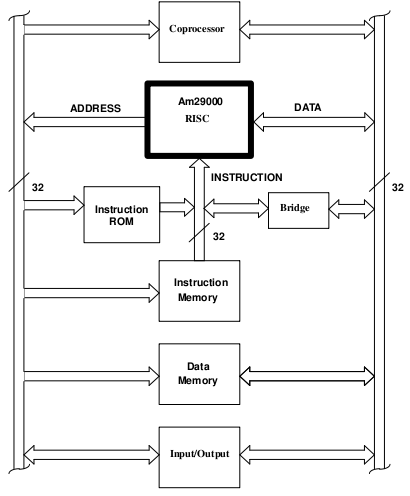

Již v předchozím textu jsme se zmínili o tom, že některé mikroprocesory z rodiny AMD 29000 (konkrétně se jedná o navzájem pinově kompatibilní čipy Am29000, Am29005 a Am29050) využívají Harvardskou architekturu, tj. architekturu, kde došlo k oddělení paměti programu od paměti dat. Díky rozdělení paměti na dvě samostatné oblasti bylo možné dosáhnout většího výpočetního výkonu, protože procesor mohl v jeden okamžik načítat kód instrukce z paměti programu a současně načítat či ukládat slovo do paměti dat. Některé procesory s Harvardskou architekturou (z nichž mnohé mají navíc architekturu RISC) jsou z tohoto důvodu vybaveny celkem čtyřmi externími sběrnicemi. První sběrnice v tomto případě slouží pro adresaci paměti programu, druhá pro přenos instrukčních slov z paměti programu do mikroprocesoru, třetí sběrnice pro adresaci paměti dat a konečně čtvrtá sběrnice pro přenos dat mezi mikroprocesorem a pamětí dat.

Obrázek 5: Sovětská varianta čipu Am2903.

Ovšem větší množství externích sběrnic vede k nutnosti použití čipového pouzdra s větším počtem vývodů, což výrobu prodražuje a současně se i snižuje poměr dobrých/špatných kusů čipů (což znamená další zdražení kvůli menší výtěžnosti). Z tohoto důvodu se konstruktéři čipů patřících do rodiny AMD 29000 rozhodli pro použití „pouze“ tří sběrnic, přičemž došlo ke sloučení adresové sběrnice paměti dat a adresové sběrnice paměti programu do jediné adresové sběrnice. Díky tomu, že procesory mají velký počet pracovních registrů a současně podporují burst režim (blokový přenos dat bez nutnosti přenosu adresy pro každé přenášené slovo), tak se počet konfliktů vzniklých při současné adresaci paměti programu a paměti dat snížil takovým způsobem, že zpomalení operací třísběrnicového procesoru oproti (teoretickému) procesoru se čtyřmi sběrnicemi dosahovalo pouze pěti procent, tj. přidání chybějící čtvrté sběrnice o šířce 32 bitů by se i přes podstatně vyšší cenu procesoru (zhruba o 15–20%) projevilo jen přibližně pětiprocentním nárůstem jeho výpočetního výkonu.

Obrázek 6: Schéma připojení procesoru AMD 29000 k pamětem a periferním zařízením pomocí trojice externích sběrnic.

Zdroj: Daniel Mann – Evaluating and Programming the 29KTM RISC Family

4. Globální a lokální registry

Procesory AMD 29000 obsahují, podobně jako další procesory s architekturou RISC, velké množství registrů. Většina registrů je interně implementována klopnými obvody se třemi porty, což mj. umožňuje, aby ihned po provedení vybrané ALU operace byla nová hodnota registru dostupná jako operand pro další instrukci (zpoždění je pouze jeden hodinový takt, stejně jako u většiny ostatních RISCových procesorů). Celou sadu registrů lze rozdělit na registry globální, registry lokální a speciální registry. Globálních registrů může být teoreticky až 128, ovšem ve skutečnosti je jich pro obecné použití použito pouze 64. Jejich jména jsou gr64 až gr127. Kromě toho mají první dva popř. první čtyři globální registry speciální význam:

| Globální registru | Význam |

|---|---|

| gr0 | použit při nepřímém adresování |

| gr1 | ukazatel na bázi zásobníku (což je vlastně index jednoho lokálního registru, od něhož se odvozují registry použité v subrutině) |

| gr2 | přítomen pouze na čipu Am29050 pro akumulaci výsledků porovnání |

| gr3 | přítomen pouze na čipu Am29050 pro akumulaci výsledků porovnání |

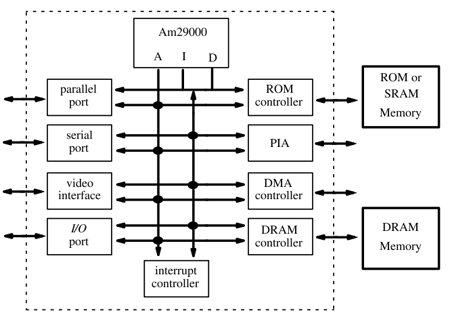

Obrázek 7: Jádro AMD 29000 použité jako mikrořadič.

Zdroj: Daniel Mann – Evaluating and Programming the 29KTM RISC Family

Lokálních registrů je 128 a jejich indexy jsou 128 až 255. Zajímavý je přístup k těmto registrům, protože při jejich adresování je v instrukci uložen offset přičítaný k bázi, která může ukazovat na libovolný z těchto registrů. Báze je uložena v globálním registru gr1, který tak vlastně slouží jako ukazatel na začátek zásobníku (protože je jeho hodnota většinou měněna při volání subrutin). Pokud je součet báze+offset větší než 127, je horní bit výsledku součtu ignorován, takže se ve skutečnosti provádí výpočet báze+offset modulo 128. Tento způsob práce s lokálními registry sice může být na první pohled poněkud krkolomný, ve skutečnosti však umožňuje mnohem větší flexibilitu při volání subrutin, než tomu je u procesorů, které využívají registrová okna pevné velikosti. Důvod je prostý – v některých případech subrutina nevyužije všechny přidělené registry v registrovém oknu, proto se soubor registrů nevyužívá optimálně. Při využití přístupu k lokálním registrům přes bázi je vhodný způsob alokace ponechán na překladači.

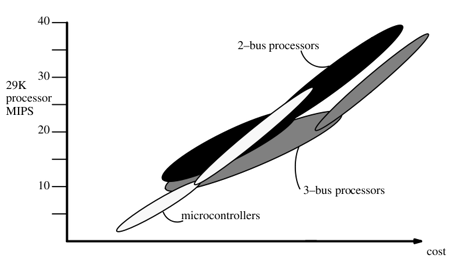

Obrázek 8: „Mapa“ ukazující cenové a výkonnostní parametry různých čipů s jádrem AMD 29000.

Zdroj: Daniel Mann – Evaluating and Programming the 29KTM RISC Family

5. Speciální registry

Kromě globálních a lokálních registrů najdeme v mikroprocesorech patřících do rodiny AMD 29000 i poměrně velké množství speciálních registrů. Jejich počet se liší podle typu mikroprocesoru i na základě toho, jaké moduly daný procesor obsahuje (velké množství speciálních registrů se například využívá v modulu MMU určeném pro řízení přístupu k paměti). V následující tabulce jsou pro ilustraci vypsána jména i popisy některých speciálních registrů dostupných na většině čipů řady 29k:

| Jméno | Zkratka | Plný název | Význam |

|---|---|---|---|

| sr1 | OPS | old processor status | původní stav procesoru; ve skutečnosti se jedná o kopii registru sr2 (CPS) při zpracování přerušení či výjimky |

| sr2 | CPS | current processor status | aktuální stav procesoru |

| sr3 | CFG | configuration control register | konfigurace procesoru |

| sr4 | CHA | channel address | řízení přístupu k datové paměti |

| sr5 | CHD | channel data | řízení přístupu k datové paměti |

| sr6 | CHC | channel control | řízení přístupu k datové paměti |

| sr7 | RBP | register bank protect | řízení přístupu k pracovním registrům pro proces běžící v uživatelském režimu (user space) |

| sr8 | TMC | timer counter | 24bitový čítač s automatickou dekrementací hodnoty v každém hodinovém cyklu |

| sr9 | TMR | timer reload value | použit v případě TMC==0 (což vygeneruje přerušení) pro naplnění nové počáteční hodnoty TMC |

| sr128 | IPA | indirect pointer A | použit při nepřímém adresování pracovních registrů |

| sr129 | IPB | indirect pointer B | použit při nepřímém adresování pracovních registrů |

| sr130 | IPC | indirect pointer C | použit při nepřímém adresování pracovních registrů |

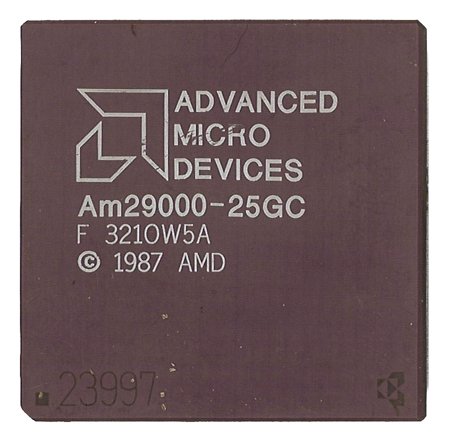

Obrázek 9: Mikroprocesor AMD 29000.

6. Formát instrukcí procesorů AMD 29000

Formát instrukcí mikroprocesorů AMD 29000 se v několika ohledech podobá formátu používaném u většiny dalších RISCových mikroprocesorů. Všechny instrukce mají konstantní šířku 32 bitů a celé instrukční slovo je rozděleno do čtyř oblastí (bitových polí), přičemž každá oblast má šířku osm bitů. Obecný formát instrukcí je následující:

------------------------------------------------------------- | 31 24 | 23 16 | 15 8 | 7 0 | ------------------------------------------------------------- | opcode | RC/CE/CNTL/I | RA/SA | RB/I | -------------------------------------------------------------

Obrázek 10: Mikroprocesor AMD 29030.

Aritmetické a logické instrukce využívají takzvaný tříadresový kód, s nímž jsme se již několikrát setkali. Instrukční slovo obsahuje v horních osmi bitech operační kód instrukce (opcode), v dalších osmi bitech je index globálního či lokálního registru, jenž slouží pro uložení výsledku instrukce (RC), následuje index registru ve funkci prvního operandu (RA) a index druhého registru, který je druhým operandem aritmetické či logické instrukce (RB):

------------------------------------------------------------- | 31 24 | 23 16 | 15 8 | 7 0 | ------------------------------------------------------------- | opcode | RC | RA | RB | -------------------------------------------------------------

Namísto indexu druhého pracovního registru lze v některých instrukcích přímo do operačního kódu uložit osmibitovou konstantu, tj. celá instrukce má následující formát (I7 .. I0 je označení osmibitové konstanty – immediate value):

------------------------------------------------------------- | 31 24 | 23 16 | 15 8 | 7 0 | ------------------------------------------------------------- | opcode | RC | RA | I7 .. I0 | -------------------------------------------------------------

Kromě osmibitové konstanty je možné u některých instrukcí použít i konstantu šestnáctibitovou. V tomto případě je však konstanta rozdělena na horních osm bitů I15 .. I8 uložených namísto bitového pole RC a dolních osm bitů I7 .. I0 uložených namísto operandu RB. Formát je tedy následující:

------------------------------------------------------------- | 31 24 | 23 16 | 15 8 | 7 0 | ------------------------------------------------------------- | opcode | I15 .. I8 | RA | I7 .. I0 | -------------------------------------------------------------

Podobný je i formát instrukcí použitý při skocích a volání subrutin. Jediná změna spočívá v tom, že nejnižší dva bity adresy jsou vždy nulové (což je logické, protože všechny instrukce jsou zarovnány na čtyři bajty), takže se tyto bity do instrukčního slova neukládají. Namísto těchto dvou nejnižších bitů tedy v instrukčním slovu zůstalo místo pro sedmnáctý a osmnáctý bit adresy:

------------------------------------------------------------- | 31 24 | 23 16 | 15 8 | 7 0 | ------------------------------------------------------------- | opcode | I17 .. I10 | RA | I9 .. I2 | -------------------------------------------------------------

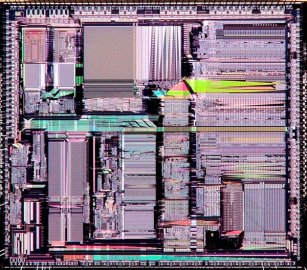

Obrázek 11: Pohled na čip AMD 29050 pod elektronovým mikroskopem s umělým dobarvením jednotlivých funkčních bloků mikroprocesoru.

7. Instrukční soubor procesorů AMD 29000

V instrukčním souboru mikroprocesorů AMD 29000 se nachází celkem 112 instrukcí, i když některé procesory nemají všechny instrukce implementovány ve svých obvodech, takže tyto instrukce musí být prováděny podprogramem. Základ instrukční sady tvoří aritmetické a logické instrukce s tříadresovým kódem – viz též předchozí kapitolu. Mezi tyto instrukce patří součet, součet s testem na přetečení při znaménkové i bezznaménkové aritmetice (při přetečení se vyvolá výjimka), rozdíl, rozdíl s testem na přetečení a taktéž násobení a dělení. Ovšem instrukce násobení a dělení nejsou na některých čipech implementovány přímo v obvodech procesoru, ale jejich spuštění vyvolá výjimku, takže je velmi snadné tyto instrukce implementovat formou vysoce optimalizovaného podprogramu (jedná se pravděpodobně o nejčistší řešení pro klasickou RISCovou architekturu). Zajímavé jsou instrukce pro porovnání dvou operandů, protože lze zvolit, do kterého globálního či lokálního registru se uloží výsledek porovnání – nepoužívá se tedy žádný speciální registr příznaků, jak je tomu u některých dalších mikroprocesorů.

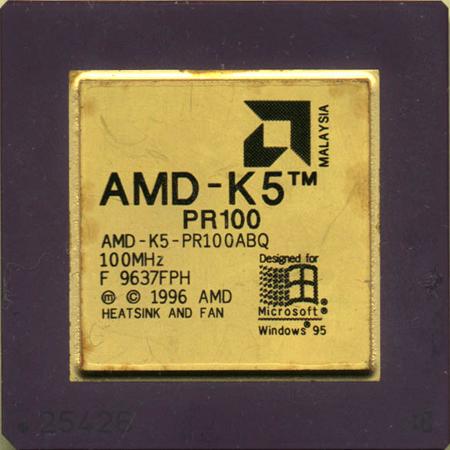

Obrázek 12: Pohled na horní část mikroprocesoru AMD K5 PR100 (výpočetní výkon tohoto mikroprocesoru by tedy měl odpovídat Pentiu 1 s hodinovou frekvencí 100 MHz).

Po instrukcích provádějících porovnání operandů s uložením výsledku porovnání do některého pracovního registru většinou následuje instrukce podmíněného skoku. Ovšem procesory AMD 29000 taktéž obsahují druhou skupinu porovnávacích instrukcí. V případě, že je podmínka splněna, pokračuje se v provádění programu, v opačném případě se vyvolá výjimka, jejíž číslo je uloženo v bitovém poli RC (bitová pole RA a RB obsahují indexy registrů, jejichž hodnoty se porovnávají). Tímto způsobem lze relativně snadno implementovat operaci assert. AMD 29000 obsahují celkem sedm bitových instrukcí s dvěma zdrojovými operandy. Jedná se o základní operace AND, OR a XOR doplněné operacemi ANDN, NAND, NOR a XNOR. Tyto instrukce jsou doplněny bitovým posunem doleva a aritmetickým i bitovým posunem doprava.

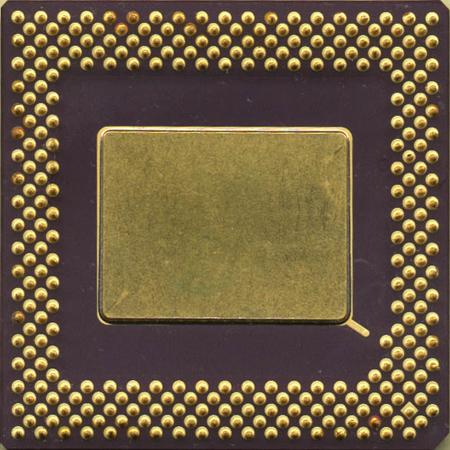

Obrázek 13: Pohled na spodní část mikroprocesoru AMD K5 PR100.

U instrukční sady s konstantní délkou všech instrukcí 32 bitů nastává problém, jakým způsobem se mohou do registrů uložit 32bitové konstanty. Již v předcházejících částech tohoto seriálu jsme viděli, že se s tímto problémem konstruktéři procesorů vypořádávají různým způsobem. U rodiny AMD 29000 se pro tento účel používá dvojice instrukcí. První instrukce CONST slouží pro naplnění spodních šestnácti bitů pracovního registru a instrukce CONSTH naopak pro naplnění horních šestnácti bitů. Formát této instrukce jsme si uvedli v předchozí kapitole – osm bitů instrukčního slova je určeno pro operační kód, dalších osm bitů pro index pracovního registru a zbylých šestnáct bitů pro konstantu. U procesoru AMD 29050 (nejvýkonnější čip z celé rodiny) je navíc implementována i instrukce CONSTN, která slouží pro načtení 16bitové konstanty do spodní poloviny vybraného pracovního registru, zatímco horních šestnáct bitů je vynulováno.

8. Od čipů AMD 29000 k mikroprocesorům AMD K5 a AMD K6

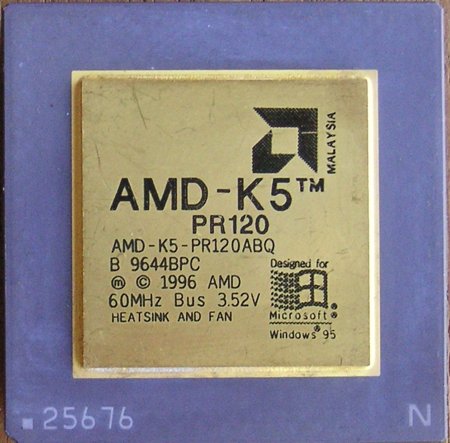

V úvodní kapitole tohoto článku jsme si řekli, že firma AMD další vývoj procesorů 29k v polovině devadesátých let minulého století pozastavila. Zajímavé však je, že mikroprocesory AMD 29000 ve skutečnosti ze světa výpočetní techniky v roce 1995 úplně nezmizely, protože relativně velká část funkčních modulů čipu AMD 29000 i jeho matematického koprocesoru byla využita v mikroprocesorech AMD K5 (začátek prodeje v roce 1996, přičemž číslo 5 značí pátou generaci procesorů x86 vyráběnou firmou AMD: Am286, Am386, Am486, Am5×86, K5). Mikroprocesory AMD K5 sice byly z programátorského hlediska plně kompatibilní s procesory řady x86, ovšem interně se CISCové instrukce transformovaly a prováděly jádrem odvozeným právě od AMD 29000. Nutno však říci, že mikroprocesor AMD K5 nebyl (přes jeho nízkou cenu) po výkonnostní ani prodejní stránce příliš úspěšný. Jedním z důvodů poměrně chladného přijetí bylo i to, že firma AMD začala používat takzvaný „PR rating“, tj. namísto údajů o hodinové frekvenci přepočítávala výkon procesoru na ekvivalentní výkon čipů Intel Pentium (toto značení se objevilo již u čipů Am5×86).

Obrázek 14: Pohled na horní část mikroprocesoru AMD K5 PR120.

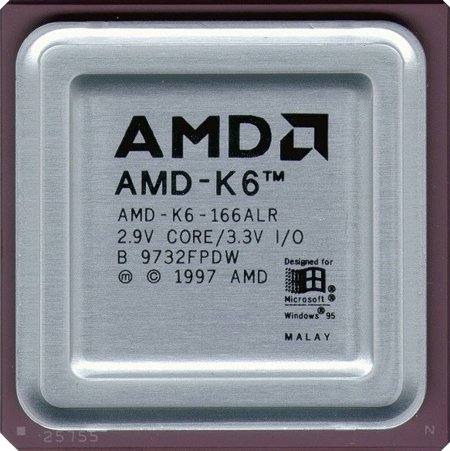

V praxi to znamenalo, že mikroprocesor prodávaný pod označením AMD K5 PR100 ve skutečnosti nevyužíval hodinovou frekvenci 100 MHz, ale pouze 66 MHz, což samozřejmě bylo uvedeno v technické dokumentaci, ale někteří novináři i uživatelé chápali použití „PR ratingu“ jako určitou formu klamání zákazníka (i když je samozřejmé, že porovnávat výkon mikroprocesorů pouze na základě hodinové frekvence není v žádném případě ten nejlepší nápad). Mnohem lepšího přijetí se v roce 1997 dočkaly až mikroprocesory AMD K6 navržené společností NexGen, která byla v roce 1996 zakoupena právě firmou AMD. I procesor AMD K6 využíval koncepci transformací CISCových instrukcí pro interní RISCové jádro, jednalo se však o zcela odlišnou technologii, což byl i jeden z důvodů vyššího výpočetního výkonu K6 (ovšem popisem různých technologií použitých v procesorech x86 se budeme zabývat až v budoucnu). Jakmile se začaly prodávat čipy AMD K6, byl další vývoj řady K5 – a tím i „platformy 29k“ ukončen.

Obrázek 15: Mikroprocesor AMD K6 se stal díky uspokojivému poměru cena/výkon oblíbeným čipem v mnoha počítačových sestavách. I tento mikroprocesor v sobě skrývá – na rozdíl od původních Pentií – RISCové jádro.

9. Odkazy na Internetu

- AMD Am29000 microprocessor family

http://www.cpu-world.com/CPUs/29000/ - AMD 29k (Streamlined Instruction Processor) ID Guide

http://www.cpushack.com/Am29k.html - AMD Am29000 (Wikipedia)

http://en.wikipedia.org/wiki/AMD_Am29000 - AMD K5 („K5“ / „5k86“)

http://www.pcguide.com/ref/cpu/fam/g5K5-c.html - Sixth Generation Processors

http://www.pcguide.com/ref/cpu/fam/g6.htm - Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - Philip Koopman: Stack Computers: the new wave

http://www.ece.cmu.edu/~koopman/stack_computers/contents.html - Hewlett Packard PA-8800 RISC (LOSTCIRCUITS)

http://www.lostcircuits.com/mambo//index.php?option=com_content&task=view&id=42&Itemid=42 - PA-RISC 1.1 Architecture and Instruction Set Reference Manual

http://h21007.www2.hp.com/portal/download/files/unprot/parisc/pa1–1/acd.pdf - Fotografie mikroprocesorů HP PA (stránka 1)

http://www.chipdb.org/cat-pa-risc-592.htm - Fotografie mikroprocesorů HP PA (stránka 2)

http://www.chipdb.org/cat-pa-risc-592.htm?page=2 - Fotografie mikroprocesorů HP PA (stránka 2)

http://www.chipdb.org/cat-pa-risc-592.htm?page=3 - PA-RISC (Wikipedia)

http://en.wikipedia.org/wiki/PA-RISC - The Great CPU List: Part VI: Hewlett-Packard PA-RISC, a conservative RISC (Oct 1986)

http://jbayko.sasktelwebsite.net/cpu4.html - HP 9000/500 FOCUS

http://www.openpa.net/systems/hp-9000_520.html - HP FOCUS Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/HP_FOCUS - HP 3000 (Wikipedia)

http://en.wikipedia.org/wiki/HP_3000 - The SPARC Architecture Manual Version 8 (manuál v PDF formátu)

http://www.sparc.org/standards/V8.pdf - The SPARC Architecture Manual Version 9 (manuál v PDF formátu)

http://developers.sun.com/solaris/articles/sparcv9.pdf - SPARC Pipelining

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/pipelining.html - SPARC Instruction

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - OpenSPARC

http://www.opensparc.net/ - History of SPARC systems 1987 to 2010

http://www.sparcproductdirectory.com/history.html - Sun-1 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-1 - Sun-2 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-2 - Sun-3 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-3 - Sun386i (Wikipedia)

http://en.wikipedia.org/wiki/Sun386i - Sun 386i/250

http://sites.inka.de/pcde/site/sun386i.html - SPARC Instruction Set

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - MIPS Architecture Overview

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/mips.html - MIPS Technologies R3000

http://www.cpu-world.com/CPUs/R3000/ - CPU-collection: IDT R3010 FPU

http://www.cpu-collection.de/?tn=0&l0=co&l1=IDT&l2=R3010+FPU - The MIPS R2000 Instruction Set

http://suraj.lums.edu.pk/~cs423a05/Reference/MIPSCodeTable.pdf - Maska mikroprocesoru RISC 1

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC1.jpg - Maska mikroprocesoru RISC 2

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC2.jpg - The MIPS Register Usage Conventions

http://pages.cs.wisc.edu/~cs354–2/beyond354/conventions.html - C.E. Sequin and D.A.Patterson: Design and Implementation of RISC I

http://www.eecs.berkeley.edu/Pubs/TechRpts/1982/CSD-82–106.pdf - Berkeley RISC

http://en.wikipedia.org/wiki/Berkeley_RISC - Great moments in microprocessor history

http://www.ibm.com/developerworks/library/pa-microhist.html - Microprogram-Based Processors

http://research.microsoft.com/en-us/um/people/gbell/Computer_Structures_Principles_and_Examples/csp0167.htm - A Brief History of Microprogramming

http://www.cs.clemson.edu/~mark/uprog.html - Architecture of the WISC CPU/16

http://www.ece.cmu.edu/~koopman/stack_computers/sec4_2.html - Zásobníkový procesor WISC CPU/16 (Root.CZ)

http://www.root.cz/clanky/programovaci-jazyk-forth-a-zasobnikove-procesory-16/#k03 - Writable instruction set, stack oriented computers: The WISC Concept

http://www.ece.cmu.edu/~koopman/forth/rochester87.pdf - The Great CPU List: Part X: Hitachi 6301 – Small and microcoded (1983)

http://jbayko.sasktelwebsite.net/cpu2.html#Sec2Part10 - What is RISC?

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/whatis/ - RISC vs. CISC

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/risccisc/ - RISC and CISC definitions:

http://www.cpushack.com/CPU/cpuAppendA.html - The Evolution of RISC

http://www.ibm.com/developerworks/library/pa-microhist.html#sidebar1 - SPARC Processor Family Photo

http://thenetworkisthecomputer.com/site/?p=243 - SPARC: Decades of Continuous Technical Innovation

http://blogs.oracle.com/ontherecord/entry/sparc_decades_of_continuous_technical - The SPARC processors

http://www.top500.org/2007_overview_recent_supercomputers/sparc_processors - Maurice V. Wilkes Home Page

http://www.cl.cam.ac.uk/archive/mvw1/ - Papers by M. V. Wilkes (důležitá je především jeho práce číslo 35)

http://www.cl.cam.ac.uk/archive/mvw1/list-of-papers.txt - Microprogram Memory

http://free-books-online.org/computers/advanced-computer-architecture/microprogram-memory/ - First Draft of a report on the EDVAC

http://qss.stanford.edu/~godfrey/vonNeumann/vnedvac.pdf - Introduction to Microcontrollers

http://www.pic24micro.com/cisc_vs_risc.html - Reduced instruction set computing (Wikipedia)

http://en.wikipedia.org/wiki/Reduced_instruction_set_computer - MIPS architecture (Wikipedia)

http://en.wikipedia.org/wiki/MIPS_architecture - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - Classic RISC pipeline (Wikipedia)

http://en.wikipedia.org/wiki/Classic_RISC_pipeline - R2000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R2000_(microprocessor) - R3000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R3000 - R4400 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R4400 - R8000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R8000 - R10000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R10000 - SPARC (Wikipedia)

http://en.wikipedia.org/wiki/Sparc - SPARC Tagged Data – otázka

http://compilers.iecc.com/comparch/article/91–04–079 - SPARC Tagged Data – odpověď #1

http://compilers.iecc.com/comparch/article/91–04–082 - SPARC Tagged Data – odpověď #2

http://compilers.iecc.com/comparch/article/91–04–088 - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Microcode (Wikipedia)

http://en.wikipedia.org/wiki/Microcode - Microsequencer (Wikipedia)

http://en.wikipedia.org/wiki/Microsequencer - Maurice Wilkes (Wikipedia)

http://en.wikipedia.org/wiki/Maurice_Wilkes - Micro-operation (Wikipedia)

http://en.wikipedia.org/wiki/Micro-operation - b16 stack processor

http://www.jwdt.com/~paysan/b16.html - Color Forth (Chuck Moore home page)

http://www.colorforth.com/ - colorForth Instructions

http://www.colorforth.com/inst.htm - SEAforth 40C18

http://www.intellasys.net/index.php?option=com_content&task=view&id=60&Itemid=75 - Bit slicing

http://en.wikipedia.org/wiki/Bit_slicing - Bitslice DES

http://www.darkside.com.au/bitslice/ - Great Microprocessors of the Past and Present: Part VII: Advanced Micro Devices Am2901, a few bits at a time …

http://www.cpushack.com/CPU/cpu1.html#Sec1Part7