Obsah

1. Krátká rekapitulace – mikrořadiče MCS-48, MCS-51, PIC a 68HCxx

2. Vlastnosti mikrořadičů vycházejících z technologií 70.let

3. Osmibitové mikrořadiče AVR – příchod technologií 90.let

4. Spojení Harvardské architektury s koncepcí RISC

5. Pracovní registry mikrořadičů AVR

6. Práce s pamětí větší než 64kB

7. Zásobník osmibitových mikrořadičů AVR

1. Krátká rekapitulace – mikrořadiče MCS-48, MCS-51, PIC a 68HCxx

V předchozích třinácti částech seriálu o architekturách počítačů jsme si popsali některé známé a dodnes velmi často používané typy osmibitových mikrořadičů. Jednalo se především o mikrořadiče firmy Intel, konkrétně o původní typ mikrořadiče Intel 8048 (MCS-48) z poloviny sedmdesátých let minulého století postavený na Harvardské architektuře, který byl o několik let později následovaný úspěšným mikrořadičem Intel 8051 (MCS-51) a jeho nepatrně vylepšenou variantou Intel 8052 (MCS-52). Firma Intel se dnes již sice výrobou osmibitových mikrořadičů nezabývá, ovšem vylepšené varianty 8051 a 8052 (například se jedná o čipy vybavené pamětí Flash nebo o optimalizované čipy s menším počtem cyklů nutných pro provádění instrukcí) jsou dodnes nabízeny mnoha dalšími výrobci. Další firmou, která se soustředila na tento segment trhu, byla společnost Microchip Technology vyrábějící již od konce sedmdesátých let minulého století osmibitové mikrořadiče nesoucí název PIC, což byla původně zkratka znamenající Programmable Interface Controller.

Obrázek 1: Pohled na počítač IMSAI 8048 bez horního krytu. Jak již název tohoto mikropočítače napovídá, je založen na osmibitovém mikrořadiči Intel 8048.

Tyto mikrořadiče se neustále vyvíjely, a to několika směry – vznikly jednodušší, levnější a méně energeticky náročné řady PIC10 a PIC12 a naopak mikrořadiče mnohem výkonnější (řady PIC16 a PIC18). Na podobném základě byly vytvořeny i čipy, které již nespadají do kategorie osmibitových mikrořadičů. Třetí řadou osmibitových mikrořadičů, kterou jsme se v předchozích částech tohoto seriálu zabývali, jsou čipy firmy Motorola. Opět se jedná o mikrořadiče mající své kořeny již v sedmdesátých letech minulého století, protože se jedná o architekturu postavenou na původním osmibitovém mikroprocesoru Motorola 6800. Prvním jednočipovým osmibitovým mikrořadičem firmy Motorola byl čip 68HC05 s jedním akumulátorem a jedním index registrem. Následovaly další typy mikrořadičů, například 68HC08, ovšem nejpoužívanějším osmibitovým mikrořadičem firmy Motorola se stal čip 68HC11 obsahující dva akumulátory (které se daly spojit do jednoho šestnáctibitového akumulátoru) a dvojici šestnáctibitových index registrů. Tento mikrořadič je používán v různých aplikacích, mj. i v satelitech (samozřejmě se jedná o verzi mající zvýšenou odolnost vůči kosmickému záření).

Obrázek 2: Jeden z dostupných vývojových kitů s mikrořadičem 8051, který je vybavený klávesnicí, dvouřádkovým displejem, sériovým portem kompatibilním s RS-232C, programátorem pamětí EPROM i EEPROM a samozřejmě i monitorem, tj. základním programovým vybavením, pomocí něhož může uživatel s vývojovým kitem pracovat.

2. Vlastnosti mikrořadičů vycházejících z technologií 70.let

V předchozí kapitole jsem na několika místech napsal, že mikrořadiče firem Intel, Microchip Technology i Motorola mají své kořeny ve druhé polovině sedmdesátých let minulého století. Tato zmínka nebyla do textu přidána kvůli nostalgickým vzpomínkám na časy, kdy programátoři znali nazpaměť celý instrukční soubor svého mikroprocesoru a o víkendech si psali pro svoji potřebu nové operační systémy (což ostatně ani přesně neodpovídá skutečnosti, protože právě tehdy se těšily velké popularitě obdivované i zatracované jazyky BASIC a Pascal). To, že všechny tři zmíněné řady osmibitových mikrořadičů jsou vlastně velmi staré, ovšem do značné míry ovlivnilo jejich architekturu. Zejména u řady MCS-48, MCS-51 a Motorola 68HCxx je patrný vliv plnohodnotných osmibitových mikroprocesorů – instrukce jsou organizovány po bajtech, přičemž první bajt vždy obsahuje instrukční kód (popř. i číslo registru) a další bajt či dvojice bajtů pak data, například osmibitovou konstantu či 8/16bitovou adresu.

Obrázek 3: Různé varianty vývojového kitu BASIC Stamp vybaveného osmibitovými mikrořadiči PIC.

I další vlastnost všech tří zmíněných architektur vychází ze stavu technologie sedmdesátých let minulého století – tyto mikrořadiče totiž obsahovaly jen minimální počet akumulátorů a index registrů. U řady MCS-51 se jednalo o jeden akumulátor A, osm v dané chvíli použitelných pracovních registrů R0 až R7 (ovšem tyto registry nemohly být použity všude tam, kde akumulátor), mikrořadiče PIC mají jediný akumulátor W (Work register) a čipy Motorola 68HC11 pak dvojici akumulátorů A a B. Pro adresování se u řady MCS-51 mohly využít osmibitové registry R0 a R1, popř. šestnáctibitový registr DPTR, zatímco u mikrořadičů 68HC11 se jednalo o dvojici plnohodnotných šestnáctibitových index registrů X a Y. Je sice pravda, že se díky použití velmi malého množství akumulátorů a pracovních registrů podařilo navrhnout instrukční sady s krátkými (jednobajtovými) instrukcemi, ovšem tato zdánlivá optimalizace přinesla mnoho problémů, především ve chvíli, kdy se i na osmibitových mikrořadičích začaly používal překladače vyšších programovacích jazyků, zejména jazyku C.

Obrázek 4: Jeden z vývojových kitů pro osmibitové mikrořadiče 68HC11.

3. Osmibitové mikrořadiče AVR – příchod technologií 90.let

Zcela odlišnou cestou se však v polovině devadesátých let minulého století vydali Alf-Egil Bogen a Vegard Wollan (v té době studenti na Norwegian Institute of Technology. Tito dva začínající konstruktéři mikrořadičů si uvědomili několik skutečností. Především se nepotvrdilo (jak mnoho technologických guru s oblibou hlásalo), že se postupně přejde na šestnáctibitové mikrořadiče, naopak poptávka po malých a levných mikrořadičích s minimální spotřebou neustále roste (příkladem jsou „programovatelné součástky“ typu PIC10 či ATtiny4). Za druhé se i na osmibitových mikrořadičích postupně začalo přecházet na vyšší programovací jazyky, což bylo mj. vynuceno i mnohem kratším vývojovým cyklem mnoha zařízení s mikrořadiči a nutností pružně reagovat na změny v konstrukci takových zařízení. Za třetí se ukázalo, že Harvardská architektura použitá u MCS-51 a taktéž u mikrořadičů PIC je v mnoha ohledech pro osmibitové mikrořadiče vhodnější, než architektura von Neumannova.

Obrázek 5: Nejmenší mikrořadiče AVR jsou představovány čipy ATtiny.

Alf-Egil Bogen a Vegard Wollan si ovšem taktéž uvědomili, že stávající architektury osmibitových mikrořadičů nejsou prakticky vůbec vhodné pro provozování programů napsaných ve vyšších programovacích jazycích. Důvody pro toto tvrzení jsou především tři: malý počet plnohodnotných pracovních registrů, nedostatečný počet index registrů, které by umožňovaly efektivně implementovat například ukazatelovou aritmetiku používanou v programovacím jazyku C nebo jednoduchou indexaci prvků polí (zde je většinou vhodné používat bázovou adresu a offset) a nakonec i malá kapacita zásobníku u některých výše zmíněných architektur (zejména PIC). Oba konstruktéři nakonec došli k tomuto závěru: Harvardská architektura se osvědčila, proto nebude špatné, když bitová šířka programové paměti u nově navrhovaných mikrořadičů bude dostatečná na to, aby bylo možné v jednom instrukčním slovu uložit jak kód instrukce, tak i její operandy. Taktéž zásobník není nutné a vhodné nijak omezovat; může růst přes celou kapacitu operační (datové) paměti. A nakonec to nejdůležitější – díky více bitům v instrukčním slovu a použitím většího množství tranzistorů na čipu mikrořadiče již není nutné šetřit počtem pracovních registrů, takže jejich počet lze zvýšit na hodnotu 32, s tím, že některé registry budou mít navíc i speciální funkci při adresování.

Obrázek 6: Bloková struktura osmibitových mikrořadičů AVR.

4. Spojení Harvardské architektury s koncepcí RISC

V osmibitových mikrořadičích AVR jsou vhodným způsobem spojeny vlastnosti Harvardské architektury a architektury RISC (i když je pravda, že počtem instrukcí se mikrořadiče AVR přibližují spíše procesorům CISC). Díky použití Harvardské architektury, tj. oddělení programové a datové paměti, bylo umožněno, aby instrukční kódy měly šířku šestnáct bitů (u několika instrukcí navíc za instrukčním kódem následují 16bitová data) načítaných v jednom taktu, zatímco aritmeticko-logická jednotka, pracovní registry i operační (datová) paměť je organizována po osmi bitech. Šestnáctibitová šířka instrukcí je dostatečná na to, aby se do jednoho instrukčního slova mohl uložit jak kód instrukce, tak i jeden či dva operandy, což v případě 32 pracovních registrů znamená 5 bitů na každý operand. Navíc, jak je ostatně u architektury RISC dobrým zvykem, je většina instrukcí pracujících pouze s pracovními registry, provedena za jediný takt, což je velký rozdíl například oproti architektuře MCS-51.

Obrázek 7: Instrukce pracující s jediným operandem mají v pěti bitech svého šestnáctibitového instrukčního slova uloženo číslo registru, který je použit jako zdrojový a současně i jako cílový operand.

To, že instrukce se dvěma operandy (ADD, ADC, AND…) mohou pracovat s libovolnou dvojicí pracovních registrů, umožňuje v praxi zmenšit celkovou délku programů, i když by se na první pohled mohlo zdát, že se kvůli šestnáctibitovým instrukcím délka kódu naopak zvýší. Skutečnost je ovšem taková, že u mikrořadičů 68HC11, MCS-51 i PIC je poměrně velká část instrukcí použita pouze pro přenos operandů do akumulátoru a následně pro uložení vypočteného výsledku z akumulátoru zpět do operační paměti (protože akumulátor musí být uvolněn pro další činnosti), zatímco značná část výpočtů na mikrořadičích AVR probíhá pouze v rámci 32 pracovních registrů. Taktéž volání procedur je jednodušší, protože některé registry mohou sloužit pro přenos parametrů procedur, stejně tak jako pro uložení návratové hodnoty. Tyto skutečnosti vedou k tomu, že délka přeloženého kódu je u mikrořadičů AVR zhruba o 20 až 40 procent menší, než v případě mikrořadičů MCS-51 (konkrétní naměřené hodnoty se samozřejmě liší podle toho, kdo porovnávání prováděl a o jakou se jednalo úlohu).

Obrázek 8: V šestnáctibitovém instrukčním slovu je dostatek místa na uložení jak čísla zdrojového registru, tak i čísla registru cílového. Z tohoto hlediska tedy mají všechny pracovní registry funkci stejnou jako akumulátor.

5. Pracovní registry mikrořadičů AVR

V předchozí kapitole jsme si řekli, že konstruktéři mikrořadičů AVR nešetřili počtem pracovních (osmibitových) registrů. Těch je dohromady 32 a v assembleru jsou označovány jmény R0 až R31. Pouze u nejmenších typů mikrořadičů ATtiny je počet pracovních registrů snížen na polovinu a jejich jména jsou R16 až R31 (toto poněkud netypické pojmenování je použito kvůli zpětné kompatibilitě s ostatními procesory AVR). Nezávisle na typu mikrořadiče má posledních šest pracovních registrů taktéž speciální význam: vždy dvojice těchto osmibitových registrů jsou spojeny takovým způsobem, že vzniknou tři šestnáctibitové registry, které je možné použít při adresování dat uložených v operační (datové) paměti či v paměti programu (zde mohou být například umístěny různé tabulky, a to jak naplněné daty, tak i cílovými adresami skoků). Způsob přiřazení šestice osmibitových pracovních registrů do trojice registrů šestnáctibitových je vypsán níže:

| Osmibitové registry | Výsledný 16bitový registr |

|---|---|

| R26+R27 | X |

| R28+R29 | Y |

| R30+R31 | Z |

Obrázek 9: Použití šestnáctibitových registrů X, Y, Z při adresování operandů uložených v paměti.

Aktuální hodnoty těchto tří šestnáctibitových registrů mohou být použity přímo pro adresování, tj. hodnota uložená v jednom z registrů X, Y, Z slouží pro načtení či uložení dat do libovolné buňky operační paměti. U některých instrukcí lze automaticky provést takzvanou post-inkrementaci nebo pre-dekrementaci obsahu adresního registru (zvýšení adresy uložené v registru po provedení operace nebo naopak snížení adresy před jejím provedením), čehož se velmi často využívá například při procházení všemi prvky pole. Jak je u RISCových architektur zvykem, jsou tyto režimy vyhrazeny především pro instrukce typu Load (LD) a Store (ST). V případě adresních registrů Y a Z je možné použít i šestibitový offset uložený přímo v šestnáctibitovém instrukčním kódu – to znamená, že instrukce využívající offset není delší než instrukce bez offsetu.

Obrázek 10: U některých instrukcí je možné adresu operandu zadat přímo za instrukčním slovem.

6. Práce s pamětí větší než 64kB

Vzhledem k tomu, že adresní registry X, Y a Z jsou „pouze“ šestnáctibitové, znamená to, že adresní rozsah (což je rozsah datové paměti, I/O prostoru i paměti programu) je omezen na 64 kB. Vzhledem k tomu, že některé mikrořadiče AVR mají paměť mnohem větší, jsou na těchto mikrořadičích navíc použity i speciální funkční registry nazvané RAMPX, RAMPY, RAMPZ a RAMPD umístěné, ostatně podobně jako i všechny další speciální funkční registry, v I/O prostoru. Obsah těchto registrů je při adresování přidán (jako vyšší bity) k šestnáctibitovým adresním registrům, čímž se rozsah adresovatelné kapacity paměti zvyšuje až na 24 bitů, samozřejmě s tím omezením, že například může být problematické procházet v programové smyčce polem přesahujícím hranici 64 kB (podobný problém je ostatně nutné řešit i u většiny dalších mikroprocesorů a mikrořadičů s podporou paměťových stránek či segmentů).

Obrázek 11: Automatická pre-dekrementace adresy při použití adresních registrů X, Y a Z.

První tři speciální funkční registry RAMPX, RAMPY a RAMPZ jsou použity při nepřímém adresování používaném v některých variantách instrukcí LD (Load) a ST (Store), tj. při takovém způsobu adresování, v němž registry X, Y či Z obsahují adresu operandu (adresa se správně vypočítá i v případě použití post-inkrementace nebo pre-dekrementace). Naproti tomu je poslední speciální funkční registr RAMPD používán při adresování přímém, zejména v instrukcích typu LDS (Load Direct from Data Space) a STS (Store Direct to Data Space), které obsahují přímou šestnáctibitovou adresu operandu. Právě k této adrese je přidán obsah registru RAMPD, čímž se zvyšuje adresový rozsah bez nutnosti používat přímo v instrukčním kódu delší adresu.

Obrázek 12: Automatická post-inkrementace adresy při použití adresních registrů X, Y a Z.

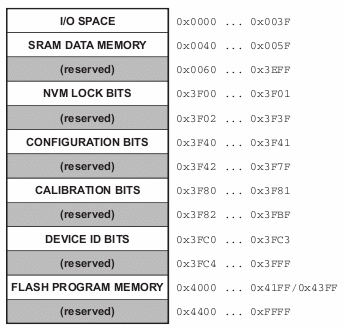

7. Zásobník osmibitových mikrořadičů AVR

Nyní si stručně popišme implementaci zásobníku na osmibitových mikrořadičích AVR. Jak jsme si již řekli v předchozích kapitolách, není velikost zásobníku prakticky nijak omezena, protože zásobník může růst až do takové velikosti, která zabere celou operační paměť, resp. maximálně 64 kB (zda je to ovšem korektní chování již musí zajistit programátor). Ukazatel na vrchol zásobníku je uložen v dvojici osmibitových speciálních funkčních registrů umístěných v I/O prostoru (SPH, SPL), jejichž obsah je možné číst a dokonce i zapisovat – opět závisí jen na programátorovi, jestli přímou změnou ukazatele na vrchol zásobníku způsobí větší škodu než užitek.

Obrázek 13: Organizace adresního prostoru u mikrořadičů AVR (rozsahy adres se samozřejmě na různých modelech odlišují).

Při volání procedury pomocí instrukce CALL (a některých dalších instrukcí využívajících relativní či nepřímé adresování) se na zásobník uloží buď dva bajty návratové adresy nebo bajty tři – některé mikrořadiče AVR totiž mohou mít až 8MB paměti programu, tj. adresní rozsah 0 až 222 (v případě paměti programu se adresují vždy šestnáctibitová slova, nikoli jednotlivé bajty).

Obrázek 14: Vzhledem k tomu, že I/O prostor má velikost jen 64 bitů, lze pro přístup ke speciálním funkčním registrům používat instrukci o délce 16 bitů.

8. Stavový registr

Posledním speciálním funkčním registrem, který si dnes popíšeme, je stavový registr nazvaný SREG. Tento registr je umístěn v I/O oblasti a jeho jednotlivé bity je možné číst i měnit buď přímo (stejně jako obsah dalších registrů), nebo lze použít speciální instrukce typu nastav bit/resetuj bit. Speciální funkční registr SREG je osmibitový, přičemž význam jeho bitů je vysvětlen v následující tabulce (povšimněte si, že jsou k dispozici i příznakové bity vhodné pro práci s čísly se znaménkem – signed integers – což pro všechny mikrořadiče neplatí):

| Index bitu | Označení | Jméno | Význam |

|---|---|---|---|

| 7 | I | Global Interrupt Enable | povolení či zákaz přerušení |

| 6 | T | Bit Copy Storage | využíván instrukcemi BLD (Bit LoaD a BST (Bit Store) pro záznam jednoho bitu |

| 5 | H | Half Carry | využíván při BCD aritmetice |

| 4 | S | Sign Bit | znaménko, vždy nastaven jako N xor V |

| 3 | V | Two's Complement Overflow Flag | příznak používaný při znaménkové aritmetice (signed integers) |

| 2 | N | Negative Flag | záporný výsledek při poslední aritmetické či logické operaci |

| 1 | Z | Zero Flag | nulový výsledek při poslední aritmetické či logické operaci |

| 0 | C | Carry Flag | přetečení z nejvyššího bitu při poslední aritmetické či logické operaci |

Obrázek 15: Další podporovaný způsob adresování, kdy se k bázové adrese uložené v některém z adresních registrů Y nebo Z přičítá šestibitový offset.

9. Odkazy na Internetu

- AVRFreaks Wiki

http://www.avrfreaks.net/wiki/index.php/Main_Page - Atmel AVR 8– and 32-bit

http://www.atmel.com/products/avr/ - tinyAVR

http://www.atmel.com/dyn/products/devices.asp?category_id=163&family_id=607&subfamily_id=791 - AT-Mini

http://www.mikroe.com/eng/products/view/649/at-mini-board/ - Arduino

http://www.arduino.cc/ - AVR Microcontroller

http://www.engineersgarage.com/articles/avr-microcontroller - Atmel AVR – Wikipedia

http://en.wikipedia.org/wiki/Atmel_AVR - AVR instruction set

http://avr.hw.cz/architektura/instukce.html - Porovnání jednotlivých procesorů AVR

http://avr.hw.cz/architektura/porovnani.html - 68HC11 Instruction Set

http://www.cs.uaf.edu/2007/fall/cs441/proj1notes/sawyer/inst.html - 68HC11 OpCode Map

http://home.earthlink.net/~tdickens/68hc11/68hc11_opcode_map.html - A Simple Robot Using the 68HC11 Processor

http://home.earthlink.net/~tdickens/68hc11/trp2/trp2.html - 68HC11 C-Compiler (Imagecraft)

http://microcontrollershop.com/product_info.php?products_id=188 - GNU Development Chain for 68HC11&68HC12

http://www.gnu.org/software/m68hc11/ - GNU C for 68HC11 – documentation

http://www.gnu.org/software/m68hc11/m68hc11_doc.html - The P-Brain tm Microcontroller Kit

http://www.futurebots.com/brain.htm - Wikipedia: Motorola 68HC05

http://en.wikipedia.org/wiki/Motorola_68HC05 - Wikipedia: Freescale 68HC08

http://en.wikipedia.org/wiki/68HC08 - Wikipedia: Freescale 68HC11

http://en.wikipedia.org/wiki/68HC11 - Wikipedia: Freescale 68HC12

http://en.wikipedia.org/wiki/Freescale_68HC12 - HC05 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684498633 - HC08 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684497663 - Digital Core Design 68HC08 – HDL IP Core

http://www.dcd.pl/acore.php?idcore=82 - Freescale 68HC11

http://www.freescale.com/webapp/sps/site/taxonomy.jsp?nodeId=01624684498635 - Lifecycle of a CPU:

http://www.cpushack.net/life-cycle-of-cpu.html - Most wanted CPU of the world:

http://www.cpu-galaxy.at/CPU/Intel%20CPU/3002–8008/4004%20Grey.jpg - Wikipedia: 6502:

http://en.wikipedia.org/wiki/6502 - The Western Design Center, Inc.:

http://www.westerndesigncenter.com/ - Apple II History Home:

http://apple2history.org/ - www.6502.org:

http://www.6502.org/ - Stránky firmy Microchip Technology

http://www.microchip.com/ - Výběr z různých modelů (osmibitových) mikrořadičů PIC

http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=2661 - Řada (rodina) osmibitových mikrořadičů PIC 10

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1009&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 12

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1001&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 14

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1008&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 16

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1002&mid=10&lang=en&pageId=74 - Další výběr z různých modelů mikrořadičů PIC

http://www.microchip.com/maps/microcontroller.aspx - PIC microcontroller (Wikipedia EN)

http://en.wikipedia.org/wiki/PIC_microcontroller - Mikrokontrolér PIC (Wikipedia CZ)

http://cs.wikipedia.org/wiki/Mikrokontrolér_PIC - FLASHFORTH for the PIC18F and the dsPIC30F

http://flashforth.sourceforge.net/ - FlashForth

http://www.sourceforge.net/projects/flashforth - Free Pic software tools

http://softwarepic.50webs.com/freesoft.html - What is Amicus?

http://www.picbasic.org/proton_lite.php - Amicus FAQ

http://www.myamicus.co.uk/faq.php?s=2e8d12e7f4c23e775776f4916876354b& - Microcontrollers development tools

http://www.gnupic.dds.nl/ - gpsim (Wikipedia EN)

http://en.wikipedia.org/wiki/Gpsim - gpsim home page

http://gpsim.sourceforge.net/gpsim.html - The FreeRTOS Project

http://www.freertos.org/ - FreeRTOS (Wikipedia)

http://en.wikipedia.org/wiki/FreeRTOS - Serial EEPROM (93C46 / 93CS46) Routines

http://www.pjrc.com/tech/8051/serial-eeprom.html - Great Microprocessors of the Past and Present (V 13.4.0)

http://jbayko.sasktelwebsite.net/cpu.html - SPI interface tutorial

http://www.best-microcontroller-projects.com/spi-interface.html - Serial Peripheral Interface Bus

http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus - EUSB to SPI bus Kit

http://www.eidusa.com/Electronics_Kits_EUSB_To_SPI_BUS.htm - SPI Block Guide V03.06, Freescale Semiconductor

http://www.freescale.com/files/microcontrollers/doc/ref_manual/S12SPIV3.pdf - What is SPI?

http://www.fpga4fun.com/SPI1.html - SPI – A simple implementation

http://www.fpga4fun.com/SPI2.html - Bit-banging

http://en.wikipedia.org/wiki/Bit-banging - Joint Test Action Group

http://en.wikipedia.org/wiki/JTAG - I2C

http://en.wikipedia.org/wiki/I2C - Seriál o programovacím jazyce Forth:

seriál o programovacím jazyce Forth - Display Data Channel

http://en.wikipedia.org/wiki/Display_Data_Channel - I2 Background

http://www.microport.tw/blognew.php?blog_no=7#theory - PIC16F87X, 28/40-pin 8-Bit CMOS FLASH Microcontrollers

Microchip Technology Inc.

http://www.microchip.com