Obsah

1. Osmibitové mikrořadiče s jádry S08 a RS08

2. Předchůdci jader S08 a RS08

5. Odlišná větev vývoje – Motorola 68HC11

6. Programátorský pohled na jádra S08

7. Adresovací režimy jader S08

8. Instrukční sada mikrořadičových jader S08

11. Aritmetické posuny, bitové posuny a rotace

12. Podmíněné i nepodmíněné skoky

13. Instrukce Booleovského procesoru

14. Přesuny dat a další operace

1. Osmibitové mikrořadiče s jádry S08 a RS08

V seriálu o architekturách počítačů a mikroprocesorů jsme si již popsali hned několik typů osmibitových mikrořadičů. Mj. se jednalo i o mikrořadiče s jádrem H8/300 a H8/300L, které byly navrženy ve společnosti Hitachi. Dnes se budeme zabývat taktéž osmibitovými mikrořadiči, které však budou od zmíněné H8/300 v mnoha ohledech odlišné (řada H8 má mnoho charakteristik RISCové architektury, což se o dnes popisovaných čipech říci nedá). Jedná se o mikrořadiče s jádry S08 popř. RS08. Tato jádra jsou odvozena od „prastarého“ mikroprocesoru Motorola 6800 (1974), na jehož základě vznikly první mikrořadiče nabízené společností Motorola. Později se celý segment výroby polovodičových čipů od Motoroly oddělil do samostatné firmy Freescale Semiconductor, která je dnes vlastněna společností NXP. Proto všechny v současnosti vyráběné osmibitové mikrořadiče s jádry S08 a RS08 nalezneme právě na stránkách této společnosti.

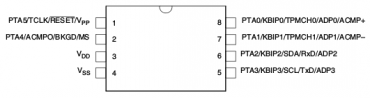

Obrázek 1: V současnosti mají nejmenší čipy s jádry RS08 pouze osm pinů a jsou tedy v tomto ohledu (a to i cenově) srovnatelné s řadou PIC10F popř. s nepatrně výkonnější řadou PIC12.

Mikrořadiče, které jsou založeny na jádrech S08 a především pak na jádrech RS08, dnes obsazují zejména tu oblast trhu, kde se požadují jednoduché mikrořadiče s malým výkonem, malými rozměry a především pak nízkým příkonem (zařízení napájená monočlánkem apod.). Těmto požadavkům odpovídá i cena čipů, která začíná na 37 centech, což znamená, že tyto čipy mohou konkurovat řadě PIC10F (což jsou vlastně „programovatelné součástky“). Podívejme se na dvě typické konfigurace:

- Jádro RS08, čip s šesti až 20 piny, frekvence CPU 10MHz, kapacita FLASH ROM 1 až 8 kB, kapacita RAM 64, 128 nebo 256 bajtů, 2–18 GPIO, komparátor, volitelný ADC, volitelný I2C, volitelný časovač a interní hodiny. Cena od 37 centů.

- Jádro S08, frekvence CPU 20 MHz až 40 MHz, počet GPIO zvýšen až na 20, přidán PWM, volitelně další časovač, SPI, SCI atd. Cena cca 68 centů a výše (podle konkrétního vybavení).

.

.

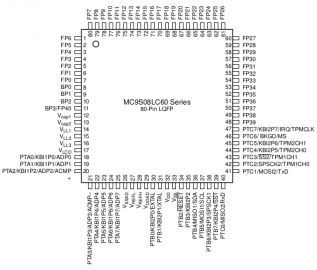

Obrázek 2: Největší čipy s jádry S08 vlastně již částečně zasahují do segmentu, v němž se setkáme se 16bitovými mikrořadiči a taktéž se slavnými RISCovými jádry ARM Cortex M (32bitové čipy).

Zdroj: Freescale Semiconductor, Data Sheet, Document Number: MC9S08LC60

2. Předchůdci jader S08 a RS08

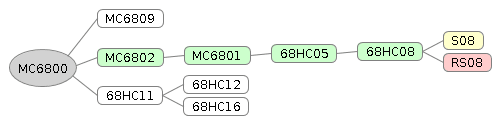

Mikrořadičová jádra S08 a RS08 jsou odvozena od mikrořadičových jader 68HC08 navržených a vyráběných ještě ve společnosti Motorola. Samotná řada 68HC08 je odvozena od starších a dnes již nevyráběných mikrořadičů s jádry 68HC05, které vznikly zjednodušením slavných osmibitových mikroprocesorů Motorola 6800. Nesmíme zapomenout ani na čip 68HC11 (taktéž již nevyvíjený), který však není s řadou S08 plně kompatibilní a je zde uveden jen pro úplnost. V následující tabulce jsou uvedeny rozdíly mezi „programátorskými modely“ jednotlivých mikrořadičů a mikroprocesorů:

| Čip | Typ | Akumulátor(y) | D=A+B (16b) | Index registr(y) | Čítač instrukcí | Zásobníkové registry | Spec. registry |

|---|---|---|---|---|---|---|---|

| MC6800 | CPU | A (8b), B (8b) | ne | X (16b) | PC (16b) | SP (16b) | CCR (6b) |

| 68HC05 | MCU | A (8b) | ne | X (8b) | PC (13b) | SP (13b) | CCR (5b) |

| 68HC08 | MCU | A (8b) | ne | H:X (16b) | PC (16b) | SP (16b) | CCR (6b) |

| 68HC11 | MCU | A (8b), B (8b) | ano | X (16b), Y (16b) | PC (16b) | SP (16b) | CCR (8b) |

| S08 | MCU | A (8b) | ne | H:X (16b) | PC (16b) | SP (16b) | CCR (6b) |

| RS08 | MCU | A (8b) | ne | X (8b) | PC (14b) + SPS (14bit) | × | CCR (2b) |

Můžeme zde vidět, že sada registrů je pojata minimalisticky, na rozdíl od již zmíněných čipů H8/300. I z tohoto důvodu nemusí být binární kód generovaný překladači céčka pro procesory S08/RS08 příliš efektivní (ostatně totéž platí i pro MCS-51 a mnohé další osmibitové mikrořadiče, které vznikly na základě architektur navržených před třiceti či dokonce čtyřiceti lety).

Poznámka: instrukční sady jsou částečně kompatibilní, ale především na úrovni zdrojových kódů (psaných v assembleru). Instrukční sady se totiž postupně vyvíjely. Největší změny se týkají použití různých adresovacích režimů, podpory pro instrukce Booleovského procesoru, rozšíření sady registrů (asi nejznámější jsou prefixy instrukcí u 68HC11 při použití index registru Y) apod.

Obrázek 3: Vývoj osmibitových a později i šestnáctibitových mikroprocesorů a mikrořadičů společnosti Motorola (později Freescale, nyní NXP).

3. Motorola 68HC05

Po vzniku osmibitového mikroprocesoru (nikoli mikrořadiče!) MC6800 firma Motorola navrhla a posléze i realizovala dvě další varianty tohoto čipu, které se některými svými vlastnostmi blížily plnohodnotným mikrořadičům. Prvním z těchto čipů byl MC6802 z roku 1977 (pozor, neplést s MOS 6502), který obsahoval kromě vlastního řadiče a CPU i 128 bajtů paměti RAM, interní oscilátor (nemusel se tedy připojovat externí zdroj hodinových signálů, postačoval pouze 4 MHz krystal pro synchronizaci) a spolu s čipem označeným MC6846 (2kB paměti ROM, osmibitový obousměrný port a časovač) bylo možné vytvořit jednoduchý dvoučipový mikropočítač, což se již v mnoha ohledech blížilo ke klasickému mikrořadiči.

Následoval čip MC6801 (číslování je, pravda, poněkud neobvyklé), který obsahoval taktéž 128 bajtů paměti RAM, navíc však na tomto čipu byla přítomna i paměť ROM s kapacitou 2 kB (zpočátku jen PROM programovatelná jedenkrát), šestnáctibitový časovač, sériový port a 31 programovatelných I/O linek (dnes by se označovaly GPIO). Jednalo se o jeden z prvních mikroprocesorů (nebo vlastně už mikrořadičů), u nichž bylo možné oba osmibitové akumulátory A a B spojit do jednoho šestnáctibitového akumulátoru označovaného písmenem D (double accumulator).

Ovšem tento čip (s cca 35000 tranzistory) byl poměrně drahý a proto se používal pouze v automobilovém průmyslu a nikoli ve spotřební elektronice. Společnost Motorola proto posléze tento čip poměrně podstatným způsobem zjednodušila a začala ho nabízet pod novým označením MC6805. Od tohoto mikrořadiče je již malý krůček k 68HC05, jímž se budeme zabývat v následujícím textu. Jak jsme si již řekli, jedná se o zjednodušenou variantu čipu MC6801, což mj. znamená, že se počet pracovních registrů zmenšil na pět (je použit jen jeden osmibitový akumulátor), indexový registr má šířku pouze osm bitů a taktéž čítač instrukcí má sníženou šířku na 13 bitů, protože paměť nainstalovaná na mikrořadiči má menší kapacitu než teoreticky dosažitelných 64 kB (podobné umělé zmenšení adresových registrů nebylo nijak neobvyklé):

| Označení | Šířka | Název registru | Význam registru |

|---|---|---|---|

| A | 8 b | accumulator A | jediný universální pracovní registr |

| X | 8 b | index register | používán při adresování operandů |

| PC | 16 b (13 použito) | program counter | používán při adresování instrukcí |

| SP | 16 b | stack pointer | použit při operacích se zásobníkem |

| CCR | 5 b | condition code register | obsahuje příznakové bity |

Obrázek 4: Interní struktura mikrořadičů M68HC05 popisovaných v této kapitole.

(Zdroj: Freescale Semiconductor, Ltd. MC68HC05B6/D Rev. 4.1 08/2005)

Instrukční soubor se u čipů 68HC05 taktéž v některých ohledech odlišoval od původní MC6800. Zejména byla přidána instrukce pro celočíselné násobení (X:A = A×X) trvající 11 cyklů a navíc se objevily instrukce (podobné instrukcím známým z MCS-51), které umožňovaly přímou manipulaci s jednotlivými bity uloženými v prvních 256 bajtech paměti: BSET (bit set), BCLR (bit clear), BRSET (branch if bit is set) a BRCLR (branch if bit is clear). Taktéž možnosti adresování byly poněkud odlišné: bylo možné provádět přímé adresování prvních 256 bajtů, rozšířené adresování (16 bitů adresy), adresování přes index registr a adresování přes index registr a osmibitový či šestnáctibitový posun (offset).

Obrázek 5: Základní zapojení mikrořadiče M68HC05.

(Zdroj: Freescale Semiconductor, Ltd. MC68HC05B6/D Rev. 4.1 08/2005)

Základní model procesoru 68HC05 měl na jediném čipu 176 bajtů RAM, 5936 bajtů ROM, 256 bajtů EEPROM, tři osmibitové I/O porty, šestnáctibitový čítač/časovač, sériové rozhraní SCI, jeden osmibitový A/D převodník a konečně modul pro PWM (pulsní šířkovou modulaci). Existovaly však i další varianty tohoto procesoru, z nichž některé měly až 32 kB ROM či EPROM, větší kapacitu paměti RAM, nainstalovanou rutinu ve firmware, která umožňovala komunikaci s PC přes sériový port (později se tato rutina vyvinula ve známé BUFFALO) atd.

Obrázek 6: Instrukční sada mikrořadiče M68HC05.

(Zdroj: Freescale Semiconductor, Ltd. MC68HC05B6/D Rev. 4.1 08/2005)

4. Motorola 68HC08

Dalším osmibitovým mikrořadičem, který byl navržen firmou Motorola a který je kupodivu nabízen dodnes (i když s celkem logickým dovětkem „Not Recommended for New Design“) je mikrořadič nesoucí označení 68HC08. Jedná se o v mnoha směrech vylepšenou variantu původního mikrořadiče 68HC05, který svým uživatelům nabízel jak větší množství vstupně-výstupních portů, více časovačů a osmikanálový analogově-digitální převodník, tak i rozšířenou kapacitu pamětí ROM a RAM.

Obrázek 7: Zapojení pinů osmibitového mikrořadiče 68HC08 popsaného v této kapitole.

(Zdroj: Technical Data – MC68HC08AB16A, Freescale Semiconductor)

Došlo i ke změně v konfiguraci registrů a rozšíření instrukční sady tohoto mikrořadiče – zejména byly přidány nové adresní režimy, které umožňovaly lépe využít zvětšenou kapacitu pamětí ROM a RAM. V následující tabulce jsou vypsány všechny registry centrální procesorové jednotky, které mohly být využity při programování v assembleru. Povšimněte si především toho, že došlo k rozšíření původně osmibitového indexového registru X na šestnáctibitový registr H:X, jehož obě osmibitové části lze v případě potřeby zpracovávat odděleně. Taktéž se rozšířila bitová šířka registrů PC a SP na plných šestnáct bitů:

| Označení | Šířka (b) | Využito bitů | Název registru | Význam registru |

|---|---|---|---|---|

| A | 8 | 8 | accumulator A | jediný universální pracovní registr |

| H:X | 16 | 16 | index register | používán při adresování operandů |

| PC | 16 | 16 | program counter | používán při adresování instrukcí |

| SP | 16 | 16 | stack pointer | použit při operacích se zásobníkem |

| CCR | 8 | 6 | condition code register | obsahuje příznakové bity |

Obrázek 8: Interní struktura mikrořadiče 68HC08.

(Zdroj: Technical Data – MC68HC08AB16A, Freescale Semiconductor)

Došlo i k rozšíření počtu příznaků uložených v registru CCR – nyní již bylo možné používat příznak V (overflow) nastavovaný mnoha aritmetickými operacemi.

Obrázek 9: Instrukční sada mikrořadiče 68HC08.

(Zdroj: Technical Data – MC68HC08AB16A, Freescale Semiconductor)

5. Odlišná větev vývoje – Motorola 68HC11

Částečně paralelně s větví 68HC05 → 68HC08 → S08 se vyvíjely mikrořadiče s označením 68HC11, které patřily mezi nejpoužívanější mikrořadiče vůbec. Jádra 68HC11 jsou sice interně, podobně jako jejich předchůdci, postavena na osmibitovém jádru (aritmeticko-logická jednotka + řadič zpracovávající instrukce s osmibitovými operačními kódy), ovšem z programátorského hlediska se jedná o čip umožňující provádění některých výpočtů i adresování se šestnáctibitovými operandy. Z tohoto hlediska se jedná o přechod mezi čistě osmibitovým a 16bitovým mikrořadičem, což může být výhodné, protože programátor není (například při adresování) omezován nutností používat osmibitové adresy či osmibitové indexové registry, ale celková cena čipu (a taktéž jeho příkon!) je díky převážně osmibitové aritmeticko-logické jednotce stále velmi příznivá, v čemž lze spatřovat jeden z důvodů, proč se osmibitové mikrořadiče stále používají.

Obrázek 10: Mikrořadič 68HC11 řady E v 64pinovém pouzdru typu QFP.

Programátoři vytvářející programy pro mikrořadič 68HC11 mohou používat dvojici osmibitových pracovních registrů A a B, které se však u některých instrukcí spojují do jediného šestnáctibitového registru nazvaného D (double accumulator). Kromě těchto registrů, které jsou převážně používány jako operandy aritmetických, logických a bitových instrukcí, je možné využít i indexové registry IX a IY (někdy jsou tyto registry pojmenované pouze X a Y), jež se používají především při adresování operandů ležících v paměti, popř. jako čítače programových smyček.

Obrázek 11: Mikrořadič 68HC11 řady E v 48pinovém pouzdru typu DIP.

V množině registrů použitelných vývojáři samozřejmě najdeme i šestnáctibitový programový čítač PC (program counter), taktéž šestnáctibitový ukazatel na vrchol zásobníku SP (stack pointer) a osmibitový registr CCR (condition codes register), který v sobě sdružuje osmici jednobitových příznaků vyžívaných například při konstrukci podmínek (což je obvykle nějaký test následovaný podmíněným skokem). Na tomto místě možná stojí za připomenutí, že mikrořadič 68HC11 je založen na původním osmibitovém mikroprocesoru MC6800; nikoli tedy na mikroprocesoru MC6809. To je trošku škoda, protože mikroprocesor MC6809 byl kvůli své téměř ortogonální instrukční sadě, existenci rozmanitých adresních režimů i přítomnosti druhého ukazatele na vrchol zásobníku U z programátorského hlediska mnohem flexibilnějším čipem (traduje se, že se jednalo o jeden z posledních mikroprocesorů s ručně optimalizovaným a „zadrátovaným“ mikrořadičem).

6. Programátorský pohled na jádra S08

Důležitá poznámka: nyní se budeme zabývat především jádry S08, protože jádra RS08 mají odlišné vlastnosti, jejichž popisu bude věnován samostatný článek.

Programátorský model mikrořadičových jader S08 se nijak zásadně neliší od 68HC08. To mj. znamená, že k dispozici je šest registrů (z toho pouze jeden akumulátor), přičemž indexové registry H a X je možné spojit a vytvořit tak šestnáctibitový indexový registr, s nímž je možné adresovat jakoukoli paměťovou buňku v rozsahu 0..64kB. Totéž platí o čítači instrukcí (PC) i ukazateli na vrchol zásobníku (SP):

| Označení | Šířka (b) | Využito bitů | Název registru | Význam registru |

|---|---|---|---|---|

| A | 8 | 8 | accumulator A | jediný universální pracovní registr |

| H:X | 16 | 16 | index register | používán při adresování operandů |

| PC | 16 | 16 | program counter | používán při adresování instrukcí |

| SP | 16 | 16 | stack pointer | použit při operacích se zásobníkem |

| CCR | 8 | 6 | condition code register | obsahuje příznakové bity |

V registru CCR jsou uloženy příznakové bity. Tento registr má sice šířku osmi bitů, ovšem jen šest bitů je skutečně využito pro uložení příznaků. Zbylé dva bity jsou nastaveny na jedničku:

| Bit# | Označení příznaku | Jméno příznaku | Význam |

|---|---|---|---|

| 7 | V | Overflow | tento příznak je nastavený při přenosu ze šestého do sedmého bitu, což v případě znaménkové aritmetiky značí přetečení hodnoty čísla do bitu vyhrazeného pro znaménko |

| 6 | × | × | neobsazeno, trvale nastaveno na 1 |

| 5 | × | × | neobsazeno, trvale nastaveno na 1 |

| 4 | H | Half-Carry Flag | nastavený při přenosu ze třetího do čtvrtého bitu; tento příznak je použit při BCD aritmetice |

| 3 | I | Interrupt Mask | příznak, pomocí něhož lze povolit či naopak zakázat maskovatelné přerušení (IRQ) |

| 2 | N | Negative Flag | tento příznak je nastaven, pokud poslední aritmetická či logická operace vygenerovala záporný výsledek, tj. bajt s nejvyšším bitem rovným jedničce (0×80 až 0×FF) |

| 1 | Z | Zero Flag | tento příznak se nastaví, pokud poslední aritmetická či logická operace vygenerovala osmibitovou hodnotu 0×00, spolu s předchozím příznakem lze zjišťovat relace typu: <0 ≤0 =0 ≥0 >0 ≠0 |

| 0 | C | Carry Flag | přetečení ze sedmého do (neexistujícího) osmého bitu při mnoha operacích (rotace, aritmetické operace); tento příznak je taktéž nastavovaný nebo nulovaný při bitových operacích v prvních 256 bajtech paměti |

Poznámka: u jader RS08 je registr CCR omezen na pouhé dva bity – Carry flag a Zero flag. Navíc zde nenalezneme registr H a i adresovací režimy jsou odlišné.

7. Adresovací režimy jader S08

V předchozí kapitole jsme mohli vidět, že počet použitelných pracovních registrů je skutečně minimální. To mj. znamená, že se registry používají poněkud odlišným způsobem, než například na klasických RISCových procesorech či na mikrořadičích, které se RISCovým procesorům alespoň částečně podobají (H8/300, MSP430 atd.). Zásadní rozdíl spočívá v tom, že jeden z operandů je typicky uložen v akumulátoru, zatímco operand druhý je umístěn v operační paměti či v ROM (to je přesný opak RISCové architektury typu load & store). Tento druhý operand musí být efektivně dosažitelný; z tohoto důvodu podporují mikrořadičová jádra S08 a RS08 velké množství adresovacích režimů. Všechny podporované adresovací režimy jsou vypsány v následující tabulce:

| # | Název | Zkratka | Stručný popis |

|---|---|---|---|

| 1 | Inherent | INH | operand je umístěn v registru |

| 2 | Relative | REL | za instrukcí je osmibitový offset připočtený k PC |

| 3 | Immediate | IMM | za instrukcí je umístěna 8bit/16bit konstanta |

| 4 | Direct | DIR | za instrukcí je umístěna osmibitová adresa do nulté stránky |

| 5 | Extended | EXT | za instrukcí je umístěna 16bitová absolutní adresa |

| 6 | Indexed | IX | operand je adresován dvojicí H:X |

| 7 | Indexed with Post Increment | IX+ | dtto, ale dvojice H:X je zvýšena o jedničku |

| 8 | Indexed, 8-Bit Offset | IX1 | k hodnotě H:X je připočten osmibitový offset |

| 9 | Indexed, 16-Bit Offset | IX2 | k hodnotě H:X je připočten 16bitový offset |

| 10 | Indexed, 8-Bit Offset with Post Increment | IX1+ | kombinace (IX+) a (IX1) |

| 11 | SP-Relative, 8-Bit Offset | SP1 | podobné (REL), ovšem offset je přičten k SP |

| 12 | SP-Relative, 16-Bit Offset | SP2 | podobné (REL), ovšem offset je přičten k SP |

Z předchozí tabulky nepřímo vyplývá, že instrukce mají proměnlivou délku, a to z toho důvodu, že za kód instrukce je nutné uložit i konstantu, osmibitový offset či šestnáctibitový offset.

8. Instrukční sada mikrořadičových jader S08

Instrukční soubor mikrořadičových jader S08 je sice relativně malý, ovšem celkový počet instrukčních kódů narůstá kvůli použití většího množství adresovacích režimů. To je ostatně jeden z důvodů, proč některé instrukce (není jich ovšem mnoho) používají jednobajtový prefix. Podobný koncept, i když pro jiné instrukce, bylo nutné použít i u výše zmiňovaných mikrořadičů 68HC11, u nichž se prefix používal u většiny instrukcí pracujících s indexovým registrem IY. U S08 naprostá většina instrukcí používá pro zakódování instrukce jediný bajt, který je v případě některých adresovacích režimů doplněn o osmibitový či šestnáctibitový offset.

V následující tabulce jsou instrukce jader S08 rozděleny podle své funkce do různých kategorií:

| Skupina | Počet instrukcí |

|---|---|

| Aritmetické instrukce | 17 |

| Logické instrukce | 5 |

| Posuny a rotace | 6 |

| Podmíněné a nepodmíněné skoky | 27 |

| Instrukce Booleovského procesoru | 4 |

| Přesuny dat a další operace | 27 |

| Celkem: | 86 |

Z dále uvedeného seznamu instrukcí je patrné, jak zásadně je instrukční sada ovlivněna tím, že namísto sady pracovních registrů je k dispozici jen jediný akumulátor. Výhodou jsou kratší instrukční kódy, zásadní nevýhodou pak nutnost použití většího množství instrukcí při implementaci algoritmů (v porovnání s RISCovými sadami).

9. Aritmetické instrukce

Aritmetické instrukce obsahují základní operace pro součet a rozdíl, přičemž u instrukcí se dvěma operandy je jedním operandem vždy akumulátor a výsledek je taktéž uložen do akumulátoru. Poněkud netypické instrukce pro součin a podíl používají registry H a X, které jsou jinak použité především pro indexování. Další dvě instrukce pak zajišťují operace s ukazatelem na vrchol zásobníku a s indexovým „dvojregistrem“:

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | ADD | součet A = A + mem |

| 2 | ADC | součet A = A + mem + carry |

| 3 | SUB | rozdíl A = A – mem |

| 4 | SBC | rozdíl A = A – mem – carry |

| 5 | MUL | součin X:A = X × A |

| 6 | DIV | podíl A = H:A / X, H = zbytek |

| 7 | AIS | SP = SP + konstanta |

| 8 | AIX | H:X = H:X + mem |

| 9 | INC | inkrementace A, X, nebo mem |

| 10 | DEC | dekrementace A, X, nebo mem |

| 11 | CLR | vynulování A, X, nebo mem |

| 12 | NEG | změna znaménka A, X, nebo mem |

| 13 | TST | porovnání A, X nebo mem s nulou |

| 14 | CMP | jako SUB, ale bez změny A |

| 15 | CPX | porovnání X s mem |

| 16 | CPHX | porovnání H:X s mem |

| 17 | DAA | korekce výsledku pro součet v kódu BCD |

Poznámka: mem je obsah paměti adresované některým z adresovacích režimů.

10. Logické instrukce

Kromě trojice klasických instrukcí AND, ORA a EOR (někde XOR) nalezneme v této skupině i instrukci pro negaci všech bitů v akumulátoru či v buňce operační paměti. Taktéž zde nalezneme instrukci BIT, která provádí tutéž operaci jako AND, ovšem změní pouze příznaky a nikoli již obsah akumulátoru:

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | AND | logický součin bit po bitu: A = A & mem |

| 2 | ORA | logické součet bit po bitu: A = A | mem |

| 3 | EOR | logická nonekvivalence: A = A ⊕ memm |

| 4 | COM | negace A, X nebo mem |

| 5 | BIT | jako AND ovšem beze změny A |

11. Aritmetické posuny, bitové posuny a rotace

Všechny instrukce pro aritmetické i bitové posuny a rotace dokážou operand posunout o jediný bit, což mj. znamená, že tyto instrukce vyžadují pouze jediný operand. U aritmetických a logických posunů se přebytečný bit přesouvá do příznaku carry, u obou instrukcí pro rotaci je carry naopak devátým bitem v „posuvném registru“:

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | LSL | logický posun doleva (lze posouvat A, X či mem) |

| 2 | LSR | logický posun doprava (-//-) |

| 3 | ASL | pouze alias k instrukci LSL |

| 4 | ASR | aritmetický posun doprava |

| 5 | ROL | rotace doleva přes příznak carry |

| 6 | ROR | rotace doprava přes příznak carry |

12. Podmíněné i nepodmíněné skoky

Jediná instrukce nepodmíněného skoku JMP je zvláštní tím, že podporuje hned pět adresovacích režimů, včetně použití indexového registru. To mj. znamená, že tuto instrukci lze použít pro implementaci rozhodovacích tabulek apod. U instrukcí podmíněného skoku se používá vždy jen relativní adresování s osmibitovým offsetem. Instrukce BRA je vlastně jen variantou instrukce JMP, ovšem s jiným adresovacím režimem:

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | JMP | nepodmíněný skok |

| 2 | BRA | nepodmíněný skok |

| 3 | BRN | v podstatě instrukce NOP |

| 4 | BEQ | skok za podmínky Z = 1 |

| 5 | BNE | skok za podmínky Z = 0 |

| 6 | BCC | skok za podmínky C = 0 |

| 7 | BCS | skok za podmínky C = 1 |

| 8 | BPL | skok za podmínky N = 0 |

| 9 | BMI | skok za podmínky N = 1 |

| 10 | BIL | skok za podmínky IRQ pin = 0 |

| 11 | BIH | skok za podmínky IRQ pin = 1 |

| 12 | BMC | skok za podmínky I = 0 |

| 13 | BMS | skok za podmínky I = 1 |

| 14 | BHCC | skok za podmínky H = 0 |

| 15 | BHCS | skok za podmínky H = 1 |

| 16 | BLT | skok za podmínky N ⊕ V = 1 |

| 17 | BLE | skok za podmínky Z | (N ⊕ V) = 1 |

| 18 | BGE | skok za podmínky N ⊕ V = 0 |

| 19 | BGT | skok za podmínky Z | (N ⊕ V) = ) |

| 20 | BLS | C | Z = 1 |

| 21 | BHI | C | Z = 0 |

| 22 | CBEQ | skok pokud A = mem |

| 23 | DBNZ | dekrementace A, X nebo M se skokem, pokud je výsledek nenulový |

| 24 | JSR | skok do podprogramu |

| 25 | BSR | relativní skok do podprogramu |

| 26 | RTS | návrat z podprogramu |

| 27 | RTI | návrat z přerušovací rutiny |

Užitečné jsou instrukce CBEQ (compare and branch if equal), což je instrukce odpovídající (až na negaci podmínky) instrukci CJNE známé z mikrořadičů MCS-51. Taktéž užitečná je instrukce DBNZ (decrement and branch if not zero), kterou lze použít pro implementaci počítaných programových smyček.

13. Instrukce Booleovského procesoru

Čtveřice instrukce je určena pro manipulaci s prvními 256 bajty paměti na úrovni jednotlivých bitů. Jedná se o instrukci BCLR sloužící pro vynulování vybraného bitu, dále o instrukci BSET pro nastavení bitu do stavu logické jedničky. Hodnotu libovolného bitu lze testovat instrukcemi BRCLR (branch if clear) a BRSET (branch if set) – na základě hodnoty příslušného bitu je proveden relativní skok v rámci ± 127 bajtů a navíc je nastaven příznak carry. Každá ze zmíněných instrukcí je v sadě instrukcí použita osmkrát, protože součástí operačního kódu je i index nastavovaného, nulovaného či testovaného bitu. Tyto instrukce jsou, jako podobně navržené instrukce u mikrořadičů MCS-51, velmi užitečné, protože do prvních 256 adres paměti jsou adresovány řídicí registry (jejichž jednotlivé bity mají různý význam) i část uživatelské RAM.

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | BCLR | vynulování bitu v paměti |

| 2 | BSET | nastavení bitu v paměti |

| 3 | BRCLR | skok, pokud je bit v paměti nulový |

| 4 | BRSET | skok, pokud je bit v paměti nastavený na 1 |

14. Přesuny dat a další operace

Zbylé instrukce slouží většinou pro přesuny dat mezi registry a pamětí, popř. pro jiné operace:

| # | Instrukce | Stručný popis |

|---|---|---|

| 1 | LDA | načtení bajtu do akumulátoru A |

| 2 | LDX | načtení bajtu do index registru X |

| 3 | LDHX | načtení dvou bajtů do H:X |

| 4 | STA | uložení akumulátoru do mem |

| 5 | STX | uložení index registru X do mem |

| 6 | STHX | uložení dvojice H:X do mem |

| 7 | TAX | přesun X=A |

| 8 | TXA | přesun A=X |

| 9 | TAP | přesun CCR=A |

| 10 | TPA | přesun A=CCR |

| 11 | TXS | přesun SP=H:X |

| 12 | TSX | přesun H:X=SP |

| 13 | NSA | prohození horních a spodních čtyř bitů v A |

| 14 | PSHA | uložení akumulátoru A na zásobník |

| 15 | PSHX | uložení index registru X na zásobník |

| 16 | PSHH | uložení index registru H na zásobník |

| 17 | PULA | obnovení akumulátoru A ze zásobníku |

| 18 | PULX | obnovení index registru X ze zásobníku |

| 19 | PULH | obnovení index registru H ze zásobníku |

| 20 | NOP | NOP (na rozdíl od BRN má jen jeden bajt) |

| 21 | SEC | nastavení C=1 |

| 22 | CLC | vynulování C=0 |

| 23 | SEI | nastavení I=1 |

| 24 | CLI | vynulování I=0 |

| 25 | BGND | pozastavení běhu programu |

| 26 | WAIT | čekání na přerušení |

| 27 | STOP | ukončení běhu programu a čekání na přerušení |

15. Odkazy na Internetu

- 8-bit S08

http://www.nxp.com/products/microcontrollers-and-processors/more-processors/8–16-bit-mcus/8-bit-s08:HCS08 - S08QB: 8-bit QB MCUs

http://www.nxp.com/products/microcontrollers-and-processors/more-processors/8–16-bit-mcus/8-bit-s08/8-bit-s08–3.6v-mcus/8-bit-qb-mcus:S08QB - 8-bit RS08

http://www.nxp.com/products/microcontrollers-and-processors/more-processors/8–16-bit-mcus/8-bit-rs08:RS08FAMILY - Wikipedia: Motorola 68HC05

http://en.wikipedia.org/wiki/Motorola_68HC05 - Wikipedia: Freescale 68HC08

http://en.wikipedia.org/wiki/68HC08 - Wikipedia: Freescale 68HC11

http://en.wikipedia.org/wiki/68HC11 - Wikipedia: Freescale 68HC12

http://en.wikipedia.org/wiki/Freescale_68HC12 - HC05 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684498633 - HC08 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684497663 - Digital Core Design 68HC08 – HDL IP Core

http://www.dcd.pl/acore.php?idcore=82 - Freescale 68HC11

http://www.freescale.com/webapp/sps/site/taxonomy.jsp?nodeId=01624684498635 - Lifecycle of a CPU:

http://www.cpushack.net/life-cycle-of-cpu.html - Great Microprocessors of the Past and Present (V 13.4.0)

http://jbayko.sasktelwebsite.net/cpu.html - SPI interface tutorial

http://www.best-microcontroller-projects.com/spi-interface.html - Serial Peripheral Interface Bus

http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus - What is SPI?

http://www.fpga4fun.com/SPI1.html - SPI – A simple implementation

http://www.fpga4fun.com/SPI2.html - Bit-banging

http://en.wikipedia.org/wiki/Bit-banging - Joint Test Action Group

http://en.wikipedia.org/wiki/JTAG - I2C

http://en.wikipedia.org/wiki/I2C - I2 Background

http://www.microport.tw/blognew.php?blog_no=7#theory - H8/3802, 38002S, 38004, 38104 (manuály k čipům)

https://www.renesas.com/en-us/document/hw-manual?hwLayerShowFlg=true&prdLayerId=184&layerName=H8%252F3802%252C%2B38002S%252C%2B38004%252C%2B38104&coronrService=document-prd-search&hwDocUrl=%2Fen-us%2Fdoc%2Fproducts%2Fmpumcu%2F001%2Frej09b0024_h83802.pdf&hashKey=c5e1fa0a18c01e6c789bc7b5c0184ed9 - Addressing mode (Wikipedia)

https://en.wikipedia.org/wiki/Addressing_mode - Renesas SH Instruction Set Summary

http://shared-ptr.com/sh_insns.html - SH-4 RISC Processor by HITACHI

http://www.cs.umd.edu/~meesh/cmsc411/website/projects/risc/risc.htm - SH-4 RISC Processor

http://www.cs.umd.edu/~meesh/cmsc411/website/projects/risc/sh-4.htm - SuperH RISC engine Family Features

https://www.renesas.com/en-us/products/microcontrollers-microprocessors/superh/superh-features.html - Orthogonal instruction set

https://en.wikipedia.org/wiki/Orthogonal_instruction_set - An introduction to the TI MSP430 low-power microcontrollers

http://mspgcc.sourceforge.net/manual/c68.html - MSP430 LaunchPad Tutorials

http://processors.wiki.ti.com/index.php/MSP430_LaunchPad_Tutorials - LaunchPad MSP430 Assembly Language Tutorial

http://robotics.hobbizine.com/asmlau.html - TI 16-bit and 32-bit microcontrollers

http://www.ti.com/lsds/ti/microcontrollers16-bit32-bit/overview.page