Obsah

1. Pohled do nitra mikroprocesoru

2. Architektury mikroprocesorů

3. Organizace cvičného mikroprocesoru

4. Registry v mikroprocesoru

5. Aritmeticko-logická jednotka

6. Dekodér instrukcí a řadič

7. Interní sběrnice

8. Instrukční sada cvičného mikroprocesoru

9. Obsah následující části seriálu

1. Pohled do nitra mikroprocesoru

Už v úvodní části tohoto seriálu jsme si ukázali a také stručně popsali architekturu počítačů navrženou Johnem von Neumannem. Připomeňme si, že se jedná o architekturu založenou na myšlence, že jak zpracovávaná či generovaná data, tak i program určený pro práci s těmito daty lze reprezentovat v paměti počítače naprosto stejným způsobem (seznamem symbolů, typicky binárních), tj. není zapotřebí nějakým zásadním způsobem provádět rozlišování mezi daty a programem – ten již nemusí být v počítači „zadrátován“, ale naopak uložen velmi flexibilním způsobem, který umožňuje poměrně jednoduše změnit funkci a tím i vlastnosti celého počítače bez nutnosti modifikovat jeho hardwarovou konfiguraci.

Procesor počítače IBM 360 evidentně ještě nebyl integrovaný do jediné součástky

Von Neumannova architektura není ve své obecnosti vůbec složitá. Celý počítač se skládá z pěti koncepčních bloků. V prvé řadě se jedná o operační paměť, ve které je uschován jak program, tak i data, se kterými program pracuje. Dále se zde nachází programový řadič řídící celý počítač i součinnost jednotlivých bloků a aritmeticko-logická jednotka (ALU), ve které jsou vykonávány aritmetické a logické operace s registry nebo přímo místy v paměti. Kromě toho jsou k tomuto systému připojeny vstupní a výstupní zařízení s různorodou funkcí. Von Neumannova architektura počítačů je zobrazena na dalším obrázku:

Von Neumannova architektura počítačů

S postupnou integrací jednotlivých částí počítače došlo i k mírné modifikaci von Neumannovy architektury, která však v žádném případě nemění její základní myšlenku. V podstatě se řadič a aritmeticko-logická jednotka sjednotily do formy jednoho čipu (integrovaného obvodu), který souhrnně nazýváme mikroprocesor. Tím se na jednu stranu (alespoň navenek) snížil počet cest, kterými mohou protékat data, na stranu druhou to přispělo k tomu, že se zjednodušil přístup k operační paměti a také ke vstupním a výstupním zařízením. Mikroprocesor má totiž vyvedeny tři typy sběrnic, přes které komunikuje se svým okolím. Jedná se o adresovou sběrnici, datovou sběrnici a řídicí sběrnici. Role těchto sběrnic bude vysvětlena příště, ale už nyní je z následujícího obrázku patrné, že vlastně došlo i k unifikaci paměti a vstupních i výstupních zařízení, což se mj. projevilo i tím, že některé mikroprocesory vůbec paměť a zařízení vzájemně nerozlišují.

Modifikovaná von Neumannova architektura počítače v případě použití mikroprocesoru

2. Architektury mikroprocesorů

V průběhu posledních více než třiceti let zkoušeli výrobci mikroprocesorů navrhovat různé varianty uspořádání jejich vnitřních částí. Toto uspořádání, které se někdy nazývá architektura mikroprocesoru, do značné míry ovlivňuje jeho vlastnosti, způsob programování i rychlost zpracování přerušení či princip připojení mikroprocesoru k operačním pamětem. Prakticky všechny mikroprocesory lze podle použité architektury rozdělit do několika skupin, které budou podrobněji popsány v dalších částech tohoto seriálu (nyní to ještě není možné, protože jsme si neřekli ani to, jak jsou implementovány základní funkce mikroprocesorů).

Strom vývoje prvních typů mikroprocesorů firem Intel, Motorola a ZiLOG

Ve stručnosti a prozatím bez vysvětlení dalších podrobností je možné říci, že existují čtyři základní principiální architektury: CISC (Complex Instruction Set Computer), RISC (Reduced Instruction Set Computer), VLIW (Very Long Instruction Word) a MISC (Minimum Instruction Set Computer). Jedná se samozřejmě o poměrně hrubé dělení, přičemž některé mikroprocesory mohou spadat do více kategorií a mnohdy také záleží na tom, jestli zkoumáme interní funkci mikroprocesorů, nebo to, jak se procesor její navenek (viz například procesory AMD, které zvnějšku zachovávají veškerou funkcionalitu procesorů řady x86, ovšem interně se jedná o RISC).

Další procesor (přesněji řečeno jeho malá část) vytvořený z diskrétních součástek v IBM s architekturou CISC

Ještě před vznikem mikroprocesorů, tj. v dobách procesorových jednotek, byly preferovány architektury CISC, tj. procesory s mnohdy velmi rozsáhlou sadou složitých instrukcí, protože se věřilo, že tyto instrukce zjednoduší práci jak programátorům, kteří píšou aplikace v assembleru, tak i překladačům. Typickým zástupcem těchto platforem je System/360 od IBM s rozsáhlou instrukční sadou, která byla na levnějších systémech z velké části emulovaná a na dražších systémech naopak nativně prováděná. Postupem času se však přišlo na to, že ani programátoři ani překladače celou instrukční sadu nevyužijí, a tak je možné mikroprocesor zjednodušit, v ideálním případě se zcela zbavit mikroprogramů (bude vysvětleno dále) a ve výsledku tak dosáhnout větší rychlosti provádění jednodušších instrukcí – zhruba takto se zrodila architektura RISC, jejíž zástupci patří mezi nejrozsáhlejší skupinu dnes vyráběných a používaných procesorů (uvádí se, že dnes je cca 70 % všech procesorů typu RISC).

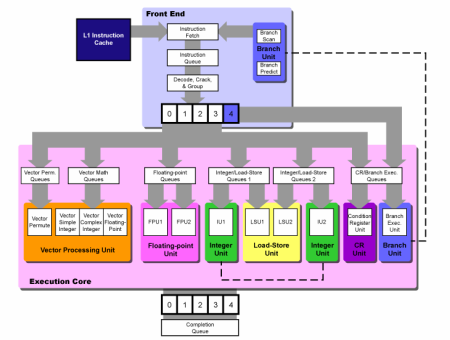

Schéma mikroprocesoru Power PC

Určitou alternativou k architekturám CISC i RISC představuje architektura MISC, která je typická především použitím instrukcí bez operandů – operandy jsou totiž známy implicitně, jelikož se většina operací provádí s hodnotami uloženými na interním či externím zásobníku (stack). Oproti RISC architektuře spočívá výhoda MISC především v menších nárocích na rychlost operačních pamětí (kratší instrukce, mnohdy odpadá nutnost použití cache pamětí) a rychlejším reakcím na přerušení (menší popř. žádná pipeline, nemusí se nikam ukládat stav procesoru atd.). Z tohoto důvodu se procesory založené na architektuře MISC používají například v oblasti řízení či real-time systémech. Architektura VLIW má v současnosti svoje místo většinou pouze ve specializovaných aplikacích, protože nároky na přenosovou rychlost operačních pamětí jsou značné, dokonce ještě větší než u klasické architektury RISC.

Zásobníkové procesory (architektura MISC) bývají interně velmi jednoduché

3. Schéma cvičného mikroprocesoru

V následujících kapitolách a později i částech tohoto seriálu si vysvětlíme princip práce mikroprocesoru, zejména způsob zpracování strojových instrukcí, které si mikroprocesor postupně načítá z operační paměti a následně je provádí. Vše si budeme ukazovat na cvičném hypotetickém mikroprocesoru, jehož schéma je zobrazeno na dalším obrázku. Jedná se o velmi jednoduchý mikroprocesor obsahující pouhé dva pracovní registry, se kterými může programátor pracovat, jednu interní sběrnici, po níž proudí jak data, tak i řídicí signály, aritmeticko-logickou jednotkou se základními operacemi (bez násobičky a děličky) a dekodérem instrukcí založeným na mikroprogramu. Z této charakteristiky je zřejmé, že se nebude jednat o zrovna nejrychlejší procesor – moderní rychlé RISC procesory mají totiž až několik desítek pracovních registrů, několik interních sběrnic, mnohdy i více aritmeticko-logických jednotek a především jsou všechny bloky rozděleny do mnoha řezů (slices), aby se v co největší míře uplatnil pipelining.

Schéma cvičného mikroprocesoru

Ve skutečnosti není nutné vlastně vůbec uvádět, kolik bitů současně může tento mikroprocesor zpracovávat, pro jednoduchost a konkrétnost však předpokládejme, že jak adresy, tak i zpracovávaná data mají jednotnou šířku 16 bitů. To znamená, že všechny uvedené registry (přesněji řečeno všechny registry kromě registru příznaků) i šířka operandů v ALU je rovna šestnácti bitům.

4. Registry v mikroprocesoru

Velmi důležitou součástí prakticky každého mikroprocesoru (a náš cvičný mikroprocesor nebude v tomto ohledu výjimkou) jsou takzvané registry. Ve své podstatě se jedná o paměti schopné uschovat vždy jedno slovo. Slovem je zde myšlena základní jednotka, se kterou mikroprocesor pracuje, většinou se jedná o šířku operandů vstupujících do aritmeticko-logické jednotky. Typická šířka slov, tj. počet současně zpracovávaných bitů, se pohybuje od 4 bitů do 128 bitů, dnes se nejčastěji jedná o 8, 16, 32 či 64 bitů. Vzhledem k tomu, že je kapacita registrů velmi malá a současně se jedná o paměť využívanou prakticky všemi instrukcemi, je většinou pro jejich vytvoření použita ta nejrychlejší dostupná technologie, což znamená, že se u běžných mikroprocesorů jedná o statické paměti, mnohdy založené na klopných obvodech typu D či JK.

V mikroprocesoru existuje více typů registrů. Náš cvičný mikroprocesor má celkem devět registrů, ovšem pouze pět z nich je viditelných programátorovi ve strojovém kódu – zbylé čtyři registry jsou interně použity mikroprocesorem pro provádění instrukcí. Na schématu je „viditelnost“ rozlišena barvou příslušného bloku.

Viditelné jsou zejména pracovní registry A a B, které se mnohdy také nazývají pojmem akumulátor, i když se v tomto případě jedná o nepřesné označení, protože ani jeden z registrů A či B není umístěn přímo na vstupu do ALU. Dále může programátor nepřímo pracovat s programovým čítačem PC a ukazatelem na vrchol zásobníku SP. Posledním viditelným registrem je registr příznaků mnohdy označovaný slovem FLAGS, písmenem F či processor status register. Registr příznaků se používá v mnoha instrukcích k různým účelům, což bude vysvětleno v příští části tohoto seriálu. Poznamenejme, že náš registr příznaků obsahuje pouze dva bity – příznak přenosu (carry flag) a příznak nulovosti (zero flag).

Pro porovnání: schéma známého mikroprocesoru Z80

5. Aritmeticko-logická jednotka

Princip aritmeticko-logické jednotky neboli ALU jsme si již vysvětlili v předchozí části tohoto seriálu, nyní tedy můžeme být stručnější. Role ALU v našem cvičném mikroprocesoru je zřejmá: na její vstup jsou připojeny dva pomocné šestnáctibitové registry (modré bloky), obsah příznaku přenosu přečtený z registru příznaků (jedná se o pouhý jeden bit) a řídicí signály přivedené přímo z interní sběrnice. Na základě řídicích signálů provede ALU požadovanou operaci a výsledek operace po několika taktech uloží do třetího pomocného registru (to je ten nejnižší modrý blok na schématu) a také do obou příznaků uložených do příznakového registru, tj. příznaku přenosu (carry flag) i příznaku nulovosti (zero flag).

Jaké operace musí ALU podporovat? Je to do značné míry určeno instrukční sadou uvedenou v osmé kapitole. Především se jedná o základní aritmetické operace (sčítání a odčítání s případným přenosem), logické operace prováděné bit po bitu, bitové posuny (bit-shift), bitové rotace a nakonec aritmetický posuv doprava. Význam těchto operací si uvedeme příště při vysvětlování provádění strojového kódu mikroprocesorem.

6. Dekodér instrukcí a řadič

Bloky dekodéru instrukcí a řadiče jsem sice zakreslil do levého horního rohu, ale ve skutečnosti se jedná o ústřední část mikroprocesoru – jeho „mozek“. Řadič pracuje na základě instrukcí, které jsou přečteny z operační paměti a přes interní sběrnici a instrukční registr vstupují do dekodéru instrukcí. Ten instrukční kód rozloží na jednotlivé části a takto předzpracovanou instrukci přenese do řadiče. Řadič je mikroprogramový (což je další pojem čekající na podrobné vysvětlení). Jeho funkce spočívá v tom, že instrukci rozloží na takzvané mikroinstrukce a jednotlivé bity mikroinstrukce následně zasílá na interní sběrnici (do její řídicí části). Tyto bity pak řídí všechny další bloky mikroprocesoru, tj. například určují, jakou operaci má provést ALU, obsah kterého pracovního registru má být poslán na vstup ALU, jaká data jsou zapsána či naopak přečtena z operační paměti atd.

Další porovnání: schéma šestnáctibitového zásobníkového mikroprocesoru bez mikroprogramového řadiče

7. Interní sběrnice

Po interní sběrnici proudí data mezi pracovními a pomocnými registry, údaje načtené z operační paměti, adresy posílané na adresní sběrnici, popř. i další údaje. Kromě toho je na této sběrnici poměrně velké množství bitových vodičů, pomocí nichž řadič určuje, kterým směrem data proudí, tj. zdrojový a cílový registr. Šířka datové a současně i adresové části interní sběrnice je šestnáct bitů, řídicí část je však mnohem širší: například pro řízení aritmeticko logické jednotky je zapotřebí pět vodičů, pro každý z pracovních i pomocných registrů dva vodiče a pro řízení externí sběrnice také dva vodiče.

8. Instrukční sada cvičného mikroprocesoru

Náš hypotetický cvičný mikroprocesor bude obsahovat celkem 32 strojových instrukcí, které jsou rozděleny do osmi skupin. Prozatím si uvedeme pouze názvy instrukcí spolu s jejich stručným popisem, do všech podrobností se všemi instrukcemi budeme zabývat v následujících částech seriálu. Jména všech dále uvedených instrukcí (přesněji řečeno mnemotechnické zkratky, které se používají v assembleru) jsou odvozena od instrukcí použitých v mikroprocesorech MOS 6502, Motorola 6800 (6809), Z8 (mikrořadič firmy ZiLOG), Z80 a Intel 8051, tedy mikroprocesorů vzniklých v dobách, kdy se ještě věci zbytečně nekomplikovaly. Mnohé z těchto mnemotechnických zkratek jsou však použity i u dalších mikroprocesorů, včetně platformy x86.

Legendární mikroprocesor MOS 6502

Na tomto místě je vhodné se zmínit o tom, že se nejedná o minimální instrukční sadu – ta má sice svůj význam, ale pro popis mnoha algoritmů (uvedených v dalších částech seriálu) mi připadlo vhodnější použít poněkud rozšířenou sadu. Pokud by někoho zajímalo, jak může vypadat minimalističtěji navržená instrukční sada, může se podívat na popis mikroprocesorů F21, P21, b16, menších typů mikrořadičů PIC a v neposlední řadě také velmi promyšlené architektury MIPS. V následující tabulce je uveden seznam všech instrukcí spolu s jejich rozdělením do již zmíněných osmi skupin:

| Kód instrukce (hex) | Mnemotechnická zkratka instrukce | Význam |

|---|---|---|

| Aritmetické instrukce | ||

| 00 | ADD | součet obsahu registrů A a B |

| 01 | ADC | součet obsahu registrů s přenosem |

| 02 | SUB | rozdíl obsahu registrů A a B |

| 03 | SBB | rozdíl obsahu registrů s výpůjčkou |

| 04 | INC | zvýšení obsahu registru A či B o 1 |

| 05 | DEC | snížení obsahu registru A či B o 1 |

| Logické instrukce | ||

| 06 | AND | operace bitového součinu nad všemi korespondujícími bity registrů A a B |

| 07 | OR | operace bitového součtu nad všemi korespondujícími bity registrů A a B |

| 08 | XOR | operace bitové nonekvivalence nad všemi korespondujícími bity registrů A a B |

| 09 | COM | negace všech bitů jednoho z registrů A či B |

| Posuvy a rotace | ||

| 0a | RL | rotace obsahu registru A či B doleva |

| 0b | RLC | rotace obsahu registru A či B doleva přes příznak přenosu |

| 0c | RR | rotace obsahu registru A či B doprava |

| 0d | RRC | rotace obsahu registru A či B doprava přes příznak přenosu |

| 0e | ASR | aritmetický posun obsah registru A či B doprava |

| Testování a porovnání | ||

| 0f | CMP | aritmetické porovnání obsahu registrů a ovlivnění příznaků |

| 10 | TEST | bitové porovnání obsahu registrů a ovlivnění příznaků |

| Přesuny mezi pamětí a registry | ||

| 11 | LD | načtení konstanty či obsahu adresy z paměti do registru A či B |

| 12 | ST | uložení obsahu registru A či B na danou adresu paměti |

| 13 | MOV | přesun dat mezi registry |

| 14 | PUSH | uložení obsahu registru A či B na zásobník |

| 15 | POP | obnovení obsahu registru A či B ze zásobníku |

| Skokové a návratové instrukce | ||

| 16 | JMP | nepodmíněný skok na zadanou adresu |

| 17 | CALL | volání podprogramu |

| 18 | RET | návrat z podprogramu |

| 19 | IRET | návrat z přerušení (interrupt) |

| 1a | JC | podmíněný skok za předpokladu, že je nastaven příznak přenosu (carry flag) |

| 1b | JNC | podmíněný skok za předpokladu, že je vynulován příznak přenosu (carry flag) |

| 1c | JZ | podmíněný skok za předpokladu, že je nastaven příznak nulovosti (zero flag) |

| 1d | JNZ | podmíněný skok za předpokladu, že je vynulován příznak nulovosti (zero flag) |

| Nezařazené zbývající instrukce | ||

| 1e | NOP | neprovádí se žádná operace, mikroprocesor přejde na další instrukci |

| 1f | HALT | mikroprocesor se zastaví a čeká na příchod externího přerušení |

9. Obsah následující části seriálu

V následující části seriálu o funkci počítačů se již můžete těšit na animace průběhu některých dějů, které se v mikroprocesoru provádí na základě algoritmu zapsaného ve strojovém kódu. Ukážeme si zejména, jakým způsobem řadič organizuje a časuje přesuny dat mezi pamětí, pracovními registry, pomocnými registry a aritmeticko-logickou jednotkou.