Obsah

1. Krátké zopakování z minula – formát instrukcí procesorů s architekturou SPARC

2. Typy instrukcí procesorů s architekturou SPARC v7

3. Aritmetické instrukce procesorů SPARC v7

4. Nenápadný vliv LISPu a Smalltalku na instrukční sadu procesorů SPARC

6. Příznakové bity a podmíněné skoky

7. Využití pracovních registrů překladači

8. Globální pracovní registry a registrová okna

1. Krátké zopakování z minula – formát instrukcí procesorů s architekturou SPARC

V předchozí části tohoto seriálu jsme se stručně seznámili s historií vývoje mikroprocesorů s architekturou SPARC verze 7. Jedná se o architekturu navrženou inženýry ze společnosti Sun Microsystems, ovšem díky poměrně širokým možnostem licencování byly mikroprocesory s touto architekturou vyráběny i mnoha dalšími firmami a dnes již je dokonce návrh interní struktury těchto procesorů dostupný ve formě otevřeného standardu. Dnes se zaměříme na popis instrukční sady SPARC v7, ovšem ještě než si vysvětlíme funkci jednotlivých instrukcí, zopakujeme si, jaké formáty instrukcí mikroprocesory s touto architekturou používají. Jak je již u klasické architektury RISC zvykem, mají všechny instrukce – včetně instrukcí obsahujících konstantu – jednotnou délku, v tomto případě 32 bitů. Prvním formátem je instrukce pro volání subrutiny (CALL, minule nesprávně označená jako instrukce skoku), v níž se používá 30bitová adresa, jež se po bitovém posuvu o dva bity stává vstupní adresou subrutiny:

+--------------------------------------------------------------+ | 01 | 30 bit constant (adresa skoku posunutá doprava o 2 bity)| +--------------------------------------------------------------+

Obrázek 1: Mikroprocesor s architekturou MicroSPARC vyráběný firmou Weitek.

Další formát je použit u podmíněných skoků. V tomto formátu je použit kód podmínky i 22 bitová konstanta, která se v případě, že je podmínka skoku splněna, vynásobí čtyřmi a následně se použije jako relativní adresa cíle skoku. Vzhledem k tomu, že se jedná o relativní adresu, je konstanta chápána jako celé číslo se znaménkem, což je nutná podmínka k tomu, aby bylo možné skok provést jak v dopředném směru (typicky při implementaci podmínky if-then-else), tak i dozadu (implementace programové smyčky):

+--------------------------------------------------------------+ | 00 |a(1)| cond(4) | op2(3)| 22 bit constant | +--------------------------------------------------------------+

Obrázek 2: Mikroprocesor s architekturou MicroSPARC vyráběný firmou Fujitsu pro Sun Microsystems.

Třetí typ instrukcí je určen pro načtení horních 22 bitů do libovolného pracovního registru (kromě registru %g0, zápis do něj je sice možný, ale nemá žádný výsledek) pomocí instrukce SETHI. Existence této instrukce byla podmíněna tím, že jiným způsobem nelze do pracovních registrů načíst celou 32bitovou konstantu, což je logické, protože 32bitové instrukční slovo obsahuje kromě konstanty i instrukční kód:

+--------------------------------------------------------------+ | 00 |rd (5) |100| 22 bit constant | +--------------------------------------------------------------+

Zbývající dva formáty instrukcí jsou použity u většiny aritmetických a logických operací. Obsahují specifikaci dvou vstupních operandů a jednoho operandu výstupního. Prvním operandem je vždy některý z pracovních registrů, druhým operandem je buď pracovní registr nebo třináctibitová konstanta:

+--------------------------------------------------------------+ | 10 | rd (5) | op3 (6) | rs1 (5) |0| unused (8) | rs2 (5) | +--------------------------------------------------------------+

+--------------------------------------------------------------+ | 11 | rd (5) | op3 (6) | rs1 (5) |1| signed 13 bit const | +--------------------------------------------------------------+

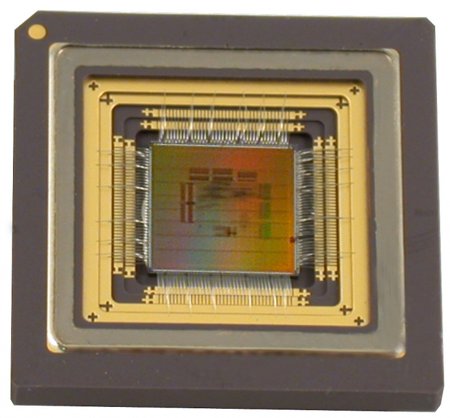

Obrázek 3: Mikroprocesor s architekturou MicroSPARC II vyráběný firmou Fujitsu pro Sun Microsystems.

2. Typy instrukcí procesorů s architekturou SPARC v7

Strojové instrukce se nemusí dělit pouze podle formátu svého instrukčního slova, ale taktéž na základě účelu, k jakému instrukce slouží. V následující tabulce jsou vypsány všechny skupiny instrukcí podporovaných mikroprocesory s architekturou SPARC v7. Ve sloupci icc je řečeno, které skupiny instrukcí mohou modifikovat příznakové bity (kterým je věnována samostatná kapitola). Důležité je taktéž to, že u instrukcí, u nichž se příznakové bity mohou měnit, lze tuto funkci zakázat, což může být v některých případech důležité, protože například logickou instrukci OR nebo aritmetickou instrukci ADD je možné využít pro naplnění spodních 13 bitů vybraného pracovního registru, aniž by výsledek této aritmetické nebo logické operace ovlivnil stav příznakových bitů (což by mohlo být nežádoucí).

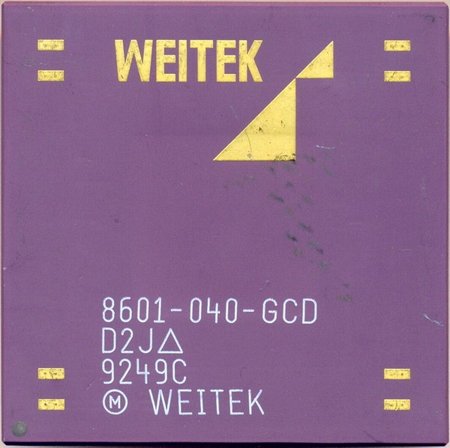

Obrázek 4: Mikroprocesor SPARC ve variantě určené pro použití v družicích. Jedná se o verzi se zvýšenou odolností proti záření.

Na tomto místě je vhodné upozornit na fakt, že kromě příznakových bitů nastavovaných CPU (resp. ALU pro celočíselné operace) se používaly příznakové bity nastavované FPU a dokonce i příznakové bity nastavované koprocesorem:

| # | Skupina instrukcí | icc | Popis |

|---|---|---|---|

| 1 | aritmetické | ano | součet a rozdíl (bez přenosu nebo s přenosem), provedení jednoho kroku násobení |

| 2 | logické | ano | šestice logických instrukcí AND, AND NOT, OR, OR NOT, XOR, XOR NOT |

| 3 | posuny | ne | logické posuny + aritmetický posun doprava (tyto instrukce skutečně neovlivňují příznakové bity) |

| 4 | načítání (LOAD) | ne | načtení jednoho bajtu, polovičního slova, celého 32 bitového slova, dvojslova s konverzí signed-unsigned |

| 5 | ukládání (STORE) | ne | uložení jednoho bajtu, polovičního slova, celého slova či dvojslova, instrukce swap, atomická instrukce pro načtení a uložení bajtu |

| 6 | podmíněné skoky | ne | s využitím registru příznaků CPU, registru příznaků FPU a registru příznaků koprocesoru |

| 7 | trap s podmínkou | ne | volání handleru s využitím registru příznaků (příznakových bitů) |

| 8 | skoky do subrutin | ne | včetně instrukcí pro posun registrového okna |

| 9 | instrukce FPU | ne | separátní množina instrukcí |

| 10 | instrukce koprocesoru | ne | separátní množina instrukcí |

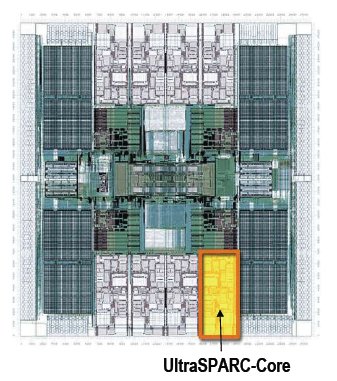

Obrázek 5: Mikroprocesory UltraSPARC jsou pokračovateli původního 32bitového mikroprocesoru SPARC.

3. Aritmetické instrukce procesorů SPARC v7

V této kapitole si vysvětlíme princip funkce některých aritmetických instrukcí, které lze najít v instrukční sadě procesorů s architekturou SPARC v7. Začněme instrukcemi pro součet a rozdíl, protože ty se svojí funkcí příliš neliší od obdobných instrukcí známých z jiných typů procesorů (až na tu maličkost, že se v případě architektury SPARC v7 jedná vždy o tříadresový kód). V této skupině instrukcí můžeme najít instrukci součtu ADD nepoužívající přenos, instrukci součtu s nastavením příznakových bitů nazvanou ADDcc, dále pak instrukci součtu s přenosem označovanou ADDX a samozřejmě i instrukci součtu s přenosem, která současně nastavuje příznakové bity ADDXcc. Podobně existuje i čtveřice instrukcí určených pro výpočet rozdílu dvou operandů: SUB, SUBcc, SUBX a SUBXcc. U všech těchto instrukcí může být druhým operandem buď libovolný pracovní registr nebo třináctibitová konstanta uložená přímo v instrukčním kódu.

Obrázek 6: Ultra SPARC II – další v minulosti velmi často používaný mikroprocesor s architekturou RISC

Zdroj: Wikipedia.

Mikroprocesory s architekturou SPARC v7 taktéž obsahovaly aritmetickou instrukci nazvanou MULScc, což je zkratka plného názvu Multiply Step and modify icc. Název této instrukce skutečně napovídá, jakou funkci tato instrukce vykonává. Nejedná se o skutečné plnohodnotné násobení (to nelze v jednou průchodu instrukční pipelinou provést), ale o jeden krok, který se při násobení dvou celých čísel provádí. Funkce vykonává čtyři činnosti:

- posun prvního operandu (částečný výsledek součinu) doprava o jeden bit s rozšířením znaménka (nejvyššího bitu) na základě znaménka předchozího mezivýsledku

- přičtení obsahu druhého operandu (násobenec) k operandu prvnímu (částečný výsledek součinu) za předpokladu, že nejnižší bit v pomocném registru Y (násobitel) je roven jedné

- posun obsahu pomocného registru Y doprava o jeden bit s nasunutím nejvyššího bitu získaného z mezivýsledku

- úprava příznakových bitů na základě operace provedené v kroku číslo 2

Podle požadavků řešené úlohy bylo možné s využitím instrukce MULScc vynásobit dvojici 32bitových čísel se 64bitovým výsledkem (horních 32 bitů bylo uloženo v pomocném registru Y), což ovšem znamenalo provést tuto instrukci až 32×. Ve skutečnosti se však v mnoha úlohách používaly menší hodnoty, což znamenalo, že se mohla násobit například jen dvě 20bitová čísla – vše záleželo na zadání úlohy, schopnostech programátora a možnostech překladače.

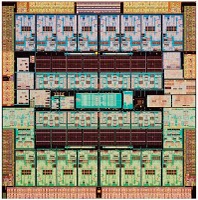

Obrázek 7: Interní struktura mikroprocesoru UltraSparc T1.

4. Nenápadný vliv LISPu a Smalltalku na instrukční sadu procesorů SPARC

Kromě osmice základních i odvozených aritmetických instrukcí se navíc v instrukční sadě procesorů SPARC v7 nachází i na první pohled poněkud zvláštní aritmetické instrukce nazvané TADDcc (Tagged Add) a TADDccTV (Tagged Add and Trap on Overflow). Tyto instrukce pracují podobně jako běžný součet, ovšem příznakový bit overflow je nastaven na logickou jedničku i v případě, že je alespoň jeden z bitů s indexem 0 či 1 libovolného operandu nenulový, druhá z těchto instrukcí navíc v tomto případě vyvolá přerušení (podobně existují i instrukce TSUBcc a TSUBccTV). Jaký je však skutečný význam těchto instrukcí?

Obrázek 8: Další varianta čipu MicroSPARC II.

V některých dialektech programovacího jazyka LISP a Smalltalk se do 32bitových slov ukládaly data i s informacemi o typu dat. Pokud byly spodní dva bity nastaveny na nulu, bylo v horních 30 bitech uloženo celé číslo (small integer), další bitové kombinace mohly znamenat ukazatel na reálné číslo či ukazatel na „velké“ celé číslo (bignum) reprezentované delší sekvencí slov. A právě u instrukcí součtu a rozdílu bylo zapotřebí jednoduše zaručit, že se součet bude provádět pouze na primitivním datovém typu small integer (z tohoto důvodu měly spodní dva bity nulovou hodnotu, aby operaci součtu/rozdílu nijak nenarušily). Tato koncepce „tagovaných dat“ v procesorech SPARC byla inspirována projektem Berkeley SOAR (Smalltalk on a RISC).

Obrázek 9: Mikroprocesor SuperSPARC.

5. Logické a bitové operace

Velmi jednoduché jsou instrukce provádějící bitové posuny. Na architektuře SPARC v7 je k dispozici instrukce určená pro posun obsahu pracovního registru doleva o zadaný počet bitů, která je nazvaná SLL (shift left logical). Obdobná instrukce pro posun obsahu pracovního registru doprava se nazývá SRL (shift right logical) a navíc je k dispozici i instrukce pro aritmetický posun doprava SAR (shift arithmetic right). Tato instrukce zachovává znaménko, tj. bit s nejvyšší váhou zůstává po posunu stále na svém místě, pouze je zkopírován do bitu nižšího. Všechny posuny jsou zadány buď pětibitovou konstantou, popř. pěti bity vybraného pracovního registru. Zajímavé je, že na rozdíl od mnoha dalších typů mikroprocesorů se v případě architektury SPARC v7 při provádění bitových a aritmetických posuvů nemění hodnota žádného příznakového bitu.

Obrázek 10: Dnes již poněkud pozapomenutý síťový počítač JavaStation vybavený mikroprocesorem MicroSPARC.

Zbývá nám popis logických instrukcí, tj. instrukcí aplikovaných na dvojici operandů bit po bitu. Jedná se o základní instrukce AND, OR a XOR, které jsou doplněny o instrukce ANDN (AND not, což znamená, že druhý operand je negován), ORN (OR not, opět je druhý operand negován) a XNOR (dtto pro základní operaci XOR). V předchozích kapitolách jsme si řekli, že u aritmetických instrukcí součtu a rozdílu (ADD a SUB) je možné zvolit, zda se mají nastavit příznakové bity. To stejné platí i pro logické instrukce, proto lze použít i „alternativní“ šestici instrukcí ANDcc, ANDNcc, ORcc, ORNcc, XORcc a XORNcc.

Obrázek 11: Další pohled na síťový počítač JavaStation.

6. Příznakové bity a podmíněné skoky

V předchozích kapitolách jsme se již několikrát zmínili o příznakových bitech. Připomeňme si, že tyto bity jsou nastavovány pouze těmito instrukcemi: ADDcc, ADDXcc, TADDcc, TADDccTV, SUBcc, SUBXcc, ANDcc, ANDNcc, ORcc, ORNcc, XORcc a XORNcc. Význam všech příznakových bitů, které jsou pojmenovány stejně, jako je tomu na mnoha dalších platformách, je vypsán v následující tabulce:

| Bit | Význam | Popis |

|---|---|---|

| c | carry | příznak přenosu z nejvyššího bitu slova |

| n | negative | příznak záporného výsledku aritmetické operace (nejvyšší bit výsledku) |

| v | overflow | příznak přetečení do znaménkového (nejvyššího) bitu výsledku |

| z | zero | příznak nulového výsledku aritmetické nebo logické (bitové) operace |

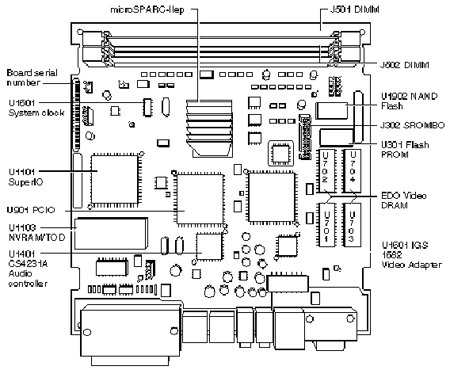

Obrázek 12: Struktura specializovaného počítače JavaEngine s mikroprocesorem MicroSPARC.

Tyto příznakové bity jsou využity v instrukcích podmíněných skoků a taktéž v podmíněném vyvolání instrukce trap (což je technologie, kterou se budeme zabývat příště). Všechny typy podmíněných skoků jsou vypsány v tabulce pod tímto odstavcem. Pokud je podmínka splněna, je cíl skoku vypočten na základě aktuální hodnoty čítače instrukcí a 22bitové konstanty uložené v instrukčním slovu. Povšimněte si toho, že v šestnácti typech skoků se nachází i instrukce BN (v podstatě odpovídá NOP) a BA (skok za každé podmínky), což je vlastnost, s níž jsme se už setkali i u některých mikroprocesorů firmy Motorola:

| Instrukce | Kód v instrukci | Operace | Provedený test |

|---|---|---|---|

| BN | 0000 | Branch Never | žádný test |

| BE | 0001 | Branch on Equal | z |

| BLE | 0010 | Branch on Less or Equal | z OR (n XOR v) |

| BL | 0011 | Branch on Less | n XOR v |

| BLEU | 0100 | Branch on Less or Equal, Unsigned | c OR z |

| BCS | 0101 | Branch on Carry Set | c |

| BNEG | 0110 | Branch on Negative | n |

| BVS | 0111 | Branch on oVerflow Set | v |

| BA | 1000 | Branch Always | žádný test |

| BNE | 1001 | Branch on Not Equal | not z |

| BG | 1010 | Branch on Greater | not(z OR (n XOR v)) |

| BGE | 1011 | Branch on Greater or Equal | not(n XOR v) |

| BGU | 1100 | Branch on Greater, Unsigned | not(c OR z) |

| BCC | 1101 | Branch on Carry Clear | not c |

| BPOS | 1110 | Branch on Positive | not n |

| BVC | 1111 | Branch on oVerflow Clear | not v |

Obrázek 13: Pohled na otevřený case specializovaného (řídicího) počítače JavaEngine s mikroprocesorem MicroSPARC. Tento počítač vznikl na základě snahy firmy Sun Microsystems o rozšíření platformy Java i do oblasti řízení.

7. Využití pracovních registrů překladači

S následující tabulkou jsme se již (i když v poněkud rozšířenější podobě) jednou setkali při porovnávání vlastností mikroprocesorů s architekturou MIPS a SPARC. V tabulce jsou vypsána čísla i aliasy (přezdívky) všech pracovních registrů, které jsou v každý okamžik viditelné a využitelné běžícím procesem. Vzhledem k tomu, že se u mikroprocesorů s architekturou SPARC využívají registrová okna, je pouze osm prvních registrů dostupných ze všech částí kódu, ostatní registry se mohou měnit v rámci posouvání registrových oken při volání subrutin a samozřejmě i při návratu ze subrutin (viz instrukce SAVE a RESTORE). Vazba mezi volanou subrutinou a volajícím programem je většinou zajištěna přes registr r[15] (%o7), volání subrutiny lze provést instrukcí CALL (s přímou adresou zadanou 30bitovou konstantou) nebo JMPL (jump and link), v níž je možné zvolit jak registr, do kterého se uloží původní hodnota čítače instrukcí, tak i cíl skoku na základě součtu obsahu dvou pracovních registrů, popř. registru a 13bitové konstanty:

| Název registru | Alias jména | Typická funkce registru |

|---|---|---|

| r[0] | %g0 | konstanta 0 |

| r[1] | %g1 | globální hodnota číslo 1 |

| r[2] | %g2 | globální hodnota číslo 2 |

| r[3] | %g3 | globální hodnota číslo 3 |

| r[4] | %g4 | globální hodnota číslo 4 |

| r[5] | %g5 | globální hodnota číslo 5 |

| r[6] | %g6 | globální hodnota číslo 6 |

| r[7] | %g7 | globální hodnota číslo 7 |

| r[8] | %o0 | návratová hodnota číslo 0 |

| r[9] | %o1 | návratová hodnota číslo 1 |

| r[10] | %o2 | návratová hodnota číslo 2 |

| r[11] | %o3 | návratová hodnota číslo 3 |

| r[12] | %o4 | návratová hodnota číslo 4 |

| r[13] | %o5 | návratová hodnota číslo 5 |

| r[14] | %sp | ukazatel na vrchol zásobníku |

| r[15] | %o7 | návratová adresa ze subrutiny |

| r[16] | %l0 | lokální data, ALU operace #0 |

| r[17] | %l1 | lokální data, ALU operace #1 |

| r[18] | %l2 | lokální data, ALU operace #2 |

| r[19] | %l3 | lokální data, ALU operace #3 |

| r[20] | %l4 | lokální data, ALU operace #4 |

| r[21] | %l5 | lokální data, ALU operace #5 |

| r[22] | %l6 | lokální data, ALU operace #6 |

| r[23] | %l7 | lokální data, ALU operace #7 |

| r[24] | %i0 | první argument funkce |

| r[25] | %i1 | druhý argument funkce |

| r[26] | %i2 | třetí argument funkce |

| r[27] | %i3 | čtvrtý argument funkce |

| r[28] | %i4 | pátý argument funkce |

| r[29] | %i5 | šestý argument funkce |

| r[30] | %fp | ukazatel na začátek rámce |

| r[31] | %i7 | sedmý argument nebo adresa adresa |

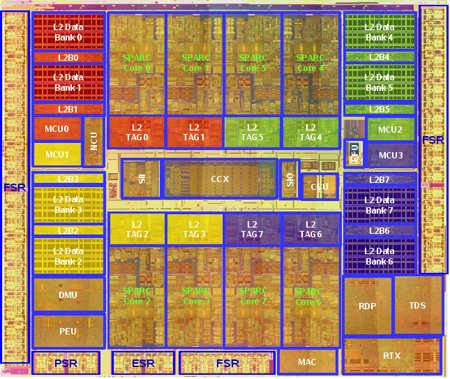

Obrázek 14: Rozmístění jednotlivých modulů, z nichž je složen mikroprocesor UltraSPARC.

8. Globální pracovní registry a registrová okna

Rozdělení pracovních registrů v subrutině (v libovolné úrovni zanoření) je následující. Prvních osm registrů je globálních, přičemž mezi tyto registry (logicky) patří i registr obsahující nulovou konstantu:

+-----------------+ | %g7 | +-----------------+ | %g6 | +-----------------+ | %g5 | +-----------------+ | %g4 | +-----------------+ | %g3 | +-----------------+ | %g2 | +-----------------+ | %g1 | +-----------------+ | %g0 (konstanta) | +-----------------+

Zbývajících 24 pracovních registrů je rozděleno na tři části: na registry, které bývají naplněné při volání subrutiny, na registry používané pro lokální data a konečně na registry plněné při volání jiné subrutiny. Programátor má sice možnost si zvolit odlišný způsob použití registrů, nicméně překladače při volání externích funkcí následující formát většinou dodržují:

+-----------------+ .............. | %i7 (ret.addr.) | : : +-----------------+ : : | %f0 (frame ptr) | : : +=================+ : registry : | %i5 (arg.) | : naplněné : +-----------------+ : při : | %i4 (arg.) | : zavolání : +-----------------+ : subrutiny : | %i3 (arg.) | : : +-----------------+ : : | %i2 (arg.) | : : +-----------------+ : : | %i1 (arg.) | : : +-----------------+ : : | %i0 (arg.) | : : +=================+ :............. | %l7 (local) | : : +-----------------+ : : | %l6 (local) | : : +-----------------+ : : | %l5 (local) | : lokální : +-----------------+ : data : | %l4 (local) | : : +-----------------+ : : | %l3 (local) | : : +-----------------+ : : | %l2 (local) | : : +-----------------+ : : | %l1 (local) | : : +-----------------+ : : | %l0 (local) | : : +=================+ :............. | %o7 (ra) | : : +-----------------+ : : | %sp (stack ptr.)| : : +-----------------+ : registry : | %o5 | : plněné : +-----------------+ : při : | %o4 | : volání : +-----------------+ : jiné : | %o3 | : subrutiny : +-----------------+ : : | %o2 | : : +-----------------+ : : | %o1 | : : +-----------------+ : : | %o0 | : : +-----------------+ :............:

Obrázek 15: Obarvené moduly mikroprocesoru UltraSPARC T3 (srovnejte s předchozím obrázkem, který se odlišuje jen v malých detailech).

9. Odkazy na Internetu

- SPARC Pipelining

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/pipelining.html - SPARC Instruction

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - OpenSPARC

http://www.opensparc.net/ - History of SPARC systems 1987 to 2010

http://www.sparcproductdirectory.com/history.html - Sun-1 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-1 - Sun-2 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-2 - Sun-3 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-3 - Sun386i (Wikipedia)

http://en.wikipedia.org/wiki/Sun386i - Sun 386i/250

http://sites.inka.de/pcde/site/sun386i.html - SPARC Instruction Set

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - MIPS Architecture Overview

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/mips.html - MIPS Technologies R3000

http://www.cpu-world.com/CPUs/R3000/ - CPU-collection: IDT R3010 FPU

http://www.cpu-collection.de/?tn=0&l0=co&l1=IDT&l2=R3010+FPU - The MIPS R2000 Instruction Set

http://suraj.lums.edu.pk/~cs423a05/Reference/MIPSCodeTable.pdf - Maska mikroprocesoru RISC 1

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC1.jpg - Maska mikroprocesoru RISC 2

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC2.jpg - The MIPS Register Usage Conventions

http://pages.cs.wisc.edu/~cs354–2/beyond354/conventions.html - C.E. Sequin and D.A.Patterson: Design and Implementation of RISC I

http://www.eecs.berkeley.edu/Pubs/TechRpts/1982/CSD-82–106.pdf - Berkeley RISC

http://en.wikipedia.org/wiki/Berkeley_RISC - Great moments in microprocessor history

http://www.ibm.com/developerworks/library/pa-microhist.html - Microprogram-Based Processors

http://research.microsoft.com/en-us/um/people/gbell/Computer_Structures_Principles_and_Examples/csp0167.htm - Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - A Brief History of Microprogramming

http://www.cs.clemson.edu/~mark/uprog.html - Architecture of the WISC CPU/16

http://www.ece.cmu.edu/~koopman/stack_computers/sec4_2.html - Zásobníkový procesor WISC CPU/16 (Root.CZ)

http://www.root.cz/clanky/programovaci-jazyk-forth-a-zasobnikove-procesory-16/#k03 - Writable instruction set, stack oriented computers: The WISC Concept

http://www.ece.cmu.edu/~koopman/forth/rochester87.pdf - The Great CPU List: Part X: Hitachi 6301 – Small and microcoded (1983)

http://jbayko.sasktelwebsite.net/cpu2.html#Sec2Part10 - What is RISC?

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/whatis/ - RISC vs. CISC

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/risccisc/ - RISC and CISC definitions:

http://www.cpushack.com/CPU/cpuAppendA.html - The Evolution of RISC

http://www.ibm.com/developerworks/library/pa-microhist.html#sidebar1 - SPARC Processor Family Photo

http://thenetworkisthecomputer.com/site/?p=243 - SPARC: Decades of Continuous Technical Innovation

http://blogs.oracle.com/ontherecord/entry/sparc_decades_of_continuous_technical - The SPARC processors

http://www.top500.org/2007_overview_recent_supercomputers/sparc_processors - Maurice V. Wilkes Home Page

http://www.cl.cam.ac.uk/archive/mvw1/ - Papers by M. V. Wilkes (důležitá je především jeho práce číslo 35)

http://www.cl.cam.ac.uk/archive/mvw1/list-of-papers.txt - Microprogram Memory

http://free-books-online.org/computers/advanced-computer-architecture/microprogram-memory/ - First Draft of a report on the EDVAC

http://qss.stanford.edu/~godfrey/vonNeumann/vnedvac.pdf - Introduction to Microcontrollers

http://www.pic24micro.com/cisc_vs_risc.html - Reduced instruction set computing (Wikipedia)

http://en.wikipedia.org/wiki/Reduced_instruction_set_computer - MIPS architecture (Wikipedia)

http://en.wikipedia.org/wiki/MIPS_architecture - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - Classic RISC pipeline (Wikipedia)

http://en.wikipedia.org/wiki/Classic_RISC_pipeline - R2000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R2000_(microprocessor) - R3000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R3000 - R4400 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R4400 - R8000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R8000 - R10000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R10000 - SPARC (Wikipedia)

http://en.wikipedia.org/wiki/Sparc - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Microcode (Wikipedia)

http://en.wikipedia.org/wiki/Microcode - Microsequencer (Wikipedia)

http://en.wikipedia.org/wiki/Microsequencer - Maurice Wilkes (Wikipedia)

http://en.wikipedia.org/wiki/Maurice_Wilkes - Micro-operation (Wikipedia)

http://en.wikipedia.org/wiki/Micro-operation - SPARC Tagged Data – otázka

http://compilers.iecc.com/comparch/article/91–04–079 - SPARC Tagged Data – odpověď #1

http://compilers.iecc.com/comparch/article/91–04–082 - SPARC Tagged Data – odpověď #2

http://compilers.iecc.com/comparch/article/91–04–088