Obsah

1. Princip statických pamětí s náhodným přístupem (SRAM)

2. Paměťová buňka statické paměti vytvořená technologií NMOS

3. Paměťová buňka statické paměti vytvořená technologií CMOS

4. Adresování paměťových buněk statických pamětí

5. Použití statických pamětí

6. Princip dynamických pamětí s náhodným přístupem (DRAM)

7. Vývoj dynamických pamětí

8. Obsah další části seriálu

1. Princip statických pamětí s náhodným přístupem (SRAM)

Dnešní popis technologií, které jsou v současnosti používané pro implementaci operačních pamětí počítačů, začíná u statických pamětí s náhodným přístupem, jež jsou většinou označovány zkratkou SRAM odvozenou od plného anglického názvu Static Random Access Memory. Na tomto místě je dobré poznamenat, že korektnější zkratka by měla znít S-RWM (Static Read-Write Memory), protože i paměti ROM, tj. Read-Only Memory, do kterých nelze zapisovat nové informace, umožňují náhodný přístup k jednou zapsaným datům. V tomto článku se však budeme držet sice ne zcela korektní, zato však vyslovitelné zkratky RAM; v případě statických pamětí pak SRAM, v případě pamětí dynamických DRAM. Statické paměti jsou v současnosti založené na matici jednobitových paměťových buněk, přičemž každá buňka je představována miniaturním bistabilním klopným obvodem sestaveným ze čtyř (technologie ECL) až šesti (CMOS, NMOS) tranzistorů.

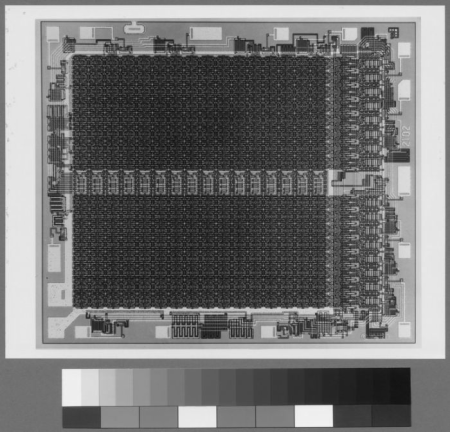

Mikroskopický snímek statické paměti s označením 2102 firmy Intel. Na pravém okraji je patrná logika výběru řádků, uprostřed rozdělení matice na dvě části o stejné kapacitě (tato část obsahuje logiku pro výběr sloupců)

Někdy se také můžeme setkat se zápisem 4-T memory cell či 6-T memory cell, přičemž ono číslo značí počet tranzistorů nutných pro implementaci jedné (jednobitové) paměťové buňky. Většinou se pro implementaci pamětí s větší kapacitou používají paměťové buňky sestavené z tranzistorů MOS s kanálem N i P (technologie CMOS), popř. pouze z tranzistorů s kanálem N (technologie NMOS). Od těchto dvou technologií jsou na základě různých (většinou patentovaných) inovací odvozeny další technologie, například HMOS (Intel), S-MOS (Texas Instruments), X-MOS (National Semiconductor) atd. Základ však zůstává stále tentýž – využití unipolárních tranzistorů s kanálem N nebo dvojic tranzistorů s kanály N a P. V následujících dvou kapitolách si popíšeme jednobitovou paměťovou buňku vytvořenou technologií NMOS i CMOS; ostatně žádný propastný rozdíl mezi nimi není.

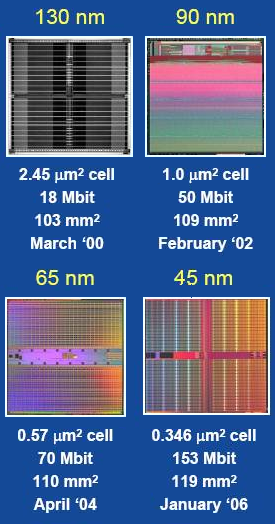

Kolorizované mikroskopické snímky testovacích vzorků pamětí firmy Intel. Z hodnot uvedených pod jednotlivými snímky je patrná zejména postupně se zmenšující plocha jedné paměťové buňky, zvyšující se rychlost čtení/zápisu a v neposlední řadě také rostoucí složitost celého čipu – u poslední paměti je matice rozdělena do čtyř bloků, přičemž každý blok obsahuje vlastní logiku pro výběr řádků a sloupců.

2. Paměťová buňka statické paměti vytvořená technologií NMOS

Na třetím obrázku je vyobrazeno principiální schéma jednobitové paměťové buňky statické paměti vytvořené technologií NMOS. Vidíme, že se buňka skládá ze šestice tranzistorů. Jedná se o tranzistory s kanálem typu N, ovšem ze schématu není patrné to, že se ve skutečnosti jedná o dva typy unipolárních tranzistorů. Zatímco tranzistory M1, M3, M5 a M6 mají obvyklý obohacovaný kanál (enhancement), dva zbylé tranzistory M2 a M4 mají kanál ochuzený (depleted). Tranzistor s ochuzeným kanálem vznikne implantací bóru s fosforem do jeho struktury, ovšem mnohem důležitější jsou jeho elektrické charakteristiky: tímto tranzistorem teče elektrický proud i v případě, že je jeho budicí napětí nulové (uzavírá se až při přivedení záporného napětí cca –1V), zatímco tranzistor s obohacovaným kanálem se chová „normálně“ – při nulovém budicím napětí jím žádný proud neteče.

Paměťová buňka statické paměti vytvořená technologií NMOS

Oba tranzistory s ochuzeným kanálem M2 a M4 slouží v paměťové buňce jako zatěžovací rezistory (s malou lokální zpětnou vazbou pro urychlení překlápění) pro tranzistory M1 a M3, které tvoří vlastní klopný obvod. Tranzistory M5 a M6 pracují v režimu nezbytných vazebních zesilovačů, kterými je paměťová buňka připojena k bitovým (sloupcovým) vodičům BL a not BL. Tyto tranzistory jsou otevřeny přivedením logické jedničky na vodič výběru řádky WL. Bitové vodiče slouží jak ke čtení hodnoty z paměťové buňky, tak i pro zápis hodnoty nové. Vždy platí, že levý bitový vodič má negovanou hodnotu vodiče pravého – to je zajištěno zesilovači umístěnými v každém sloupci paměťových buněk (liché zesilovače pracují v přímém režimu, sudé v režimu inverzním). Pokud se má bitová hodnota do buňky zapisovat, je na příslušný řádkový vodič WL přivedena logická jednička, která otevře oba vazební zesilovače a následně se pomocí sloupcových vodičů, na které jsou připojeny sloupcové zesilovače, provede zápis. Čtení opět probíhá přivedením logické jedničky na řádkový vodič WL, tentokrát jsou ovšem sloupcové zesilovače zapojeny opačně – zesilují hodnotu přečtenou z paměťové buňky a posílají ji na datový vývod paměti.

Zhruba takto může vypadat paměťová buňka při jejím vytvoření (napaření) na waferu (základu čipu)

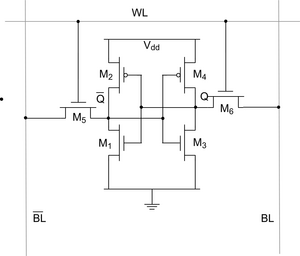

3. Paměťová buňka statické paměti vytvořená technologií CMOS

Principiální schéma jednobitové paměťové buňky statické paměti vytvořené technologií CMOS je zobrazeno na pátém obrázku. Z tohoto obrázku je patrné, že se paměťová buňka CMOS příliš neliší od buňky NMOS. V podstatě jediný rozdíl spočívá v odlišném zapojení tranzistorů M2 a M4, které slouží, jak již víme, jako zatěžovací rezistory, které ovšem mají díky lokální záporné zpětné vazbě urychlující účinek na překlápění bistabilního klopného obvodu v případě, že se zapisuje opačná bitová hodnota, než je v buňce v daném čase uložena. V případě buňky CMOS můžeme na schématu nalézt tři navzájem propojené bloky. Jsou jimi vlastní klopný obvod realizující paměťovou funkci a potom dva invertující protitaktní zesilovače tvořené dvojicí M2+M1 a M4+M3. Právě díky tomuto zapojení získávají obvody CMOS svou typickou vlastnost – pokud se v nich nemění stav logických úrovní, mají prakticky nulový odběr, protože invertujícím protitaktním zesilovačem žádný proud téct nemůže – vždy je jeden z jeho tranzistorů uzavřený. Jedině při změně úrovně je nutné do izolovaného hradla přivést popř. odvést elektrony.

Paměťová buňka statické paměti vytvořená technologií CMOS

4. Adresování paměťových buněk statických pamětí

Již v předchozích kapitolách bylo naznačeno, jakým způsobem jsou paměťové buňky v paměti uspořádány. Jedná se o dvourozměrnou mřížku tvořenou právě jednobitovými paměťovými buňkami, mezi nimiž jsou rozmístěny řádkové a sloupcové vodiče a samozřejmě i vodiče sloužící k napájení (Vdd) a uzemnění jednotlivých klopných obvodů (je zde využito několik na sobě napařených vodivých vrstev). Při čtení nebo zápisu hodnoty se nejprve vybere celý řádek paměťových buněk (těch může být i několik tisíc) a posléze se provede buď zápis přivedením příslušných signálů (hodnoty bitu a jeho negace) na sloupcové vodiče nebo se naopak ze sloupcových vodičů logická hodnota přečte, přičemž čtení je v tomto případě nedestruktivní – nemění hodnotu uloženou v paměťové buňce, což je jeden z rozdílů mezi SRAM a DRAM. Čtení či zápis je možné provádět paralelně pro celý řádek paměťových buněk, což může být v některých aplikacích s výhodou využito.

Takto naznačená struktura paměti je sice ta nejjednodušší možná, ovšem používá se (přesněji řečeno používala se) pouze u pamětí s velmi malou kapacitou. Problém představují především zesilovače na sloupcových (bitových) i řádkových vodičích, které se nesnadno implementují v případě, že mají obsloužit velké množství paměťových buněk – projevuje se zde zvýšená zátěž připojená na jejich výstupy, ale i parazitní kapacity, zpoždění signálů atd. Z tohoto důvodu jsou prakticky všechny větší paměti SRAM vytvořeny z několika pravidelných mřížek, které tak tvoří blokové struktury. Podobné metody jsou mimochodem použity i u dynamických pamětí DRAM popsaných v dalším textu. Z hlediska technika, který paměťové čipy využije ve svém zapojení či programátora se však jedná o skrytou záležitost, která se prakticky nijak neprojeví na vnější funkci paměti – ta se stále chová tak, jakoby uvnitř obsahovala jedinou obrovskou pravidelnou mřížku jednobitových paměťových buněk.

5. Použití statických pamětí

Z pohledu zapojení statických pamětí do paměťového subsystému počítače se jedná o jeden z nejjednodušších typů pamětí, společně s paměťmi typu ROM, PROM a EPROM. Existují paměti SRAM, které mají datové a adresní vodiče uzpůsobené konkrétnímu typu či rodině mikroprocesorů. Můžeme se tak setkat s čipy, které mají vyvedeno osm datových vodičů a je je možné použít například spolu s osmibitovými mikrořadiči. Vyšší počet datových vodičů má však za následek potřebu většího množství celkového počtu pinů (kontaktů), které musí paměťový čip obsahovat, protože adresovatelná kapacita je rovna c=d×2a, kde d je počet datových vodičů a a je počet vodičů adresových. Z tohoto důvodu je výhodnější, aby se počet adresových vodičů zvyšoval na úkor vodičů datových až do mezní situace, kdy zbývá pouhý jeden datový vodič (celkový počet pinů čipu má totiž nezanedbatelný vliv jak na jeho cenu, tak i cenu a spolehlivost výsledného zařízení). Paměti s touto strukturou se poté zapojují paralelně až do chvíle, kdy dosáhnou potřebné šířky slova, které lze přečíst či zapsat v jednom taktu současně pro všechny čipy.

Poměrně velká popularita pamětí SRAM spočívá v tom, že se o ně samotný mikroprocesor ani další podpůrné obvody prakticky nemusí starat – postačuje je (zjednodušeně a poněkud obrazně řečeno) připojit na datovou a adresovou sběrnici, samozřejmě s ohledem na elektrické i časové charakteristiky a pomocí signálu WE (popřípadě dvojice signálů RD a WR) řídit čtení a zápis. Z tohoto důvodu se tyto paměti velmi často využívají v různých jednoúčelových a doma vyrobených zařízeních, především v případech, kdy není zapotřebí použít čipy s velkou kapacitou. Nectností SRAM je totiž jejich poměrně velká cena, zejména v porovnání s DRAM (+ FLASH), což je daň za to, že je na jednu paměťovou buňku nutné použít šest tranzistorů zabírajících relativně velkou plochu čipu. CMOS SRAM se používají i všude tam, kde je nutné provádět pravidelné zápisy a přitom použít čip s co nejmenší spotřebou. Příkladem je konfigurace BIOSu počítače, ve které je mj. ukládán i údaj z hodin reálného času – zde by použití jiné technologie, například FLASH, nebylo vhodné.

Poměrně typické rozmístění vývodů u pamětí typu SRAM. Zde se jedná o paměť s organizací 16K×1 bit, tj. pro adresování je zapotřebí 14 pinů A0 až A13 a jeden pin pro vstup DIN a výstup DOUT (v případě potřeby může být vstup i výstup kombinovaný do jediného pinu DIN+DOUT). Signálem WE se řídí čtení či zápis dat, signálem CS lze paměť deaktivovat, tj. převést do režimu, kdy nereaguje na žádné jiné signály, ovšem obsah paměťových buněk přitom zůstává zachován.

6. Princip dynamických pamětí s náhodným přístupem (DRAM)

V běžných osobních počítačích je operační paměť v současnosti vytvořena pomocí dynamických pamětí DRAM. Ty se principem své „paměťové“ funkce dosti zásadním způsobem odlišují od statických pamětí; především v tom, že se hodnoty jednotlivých bitů neuchovávají jako stav bistabilního klopného obvodu, ale pomocí malého náboje uloženého v kondenzátoru (přesněji řečeno v takové struktuře na čipu, která se chová jako kondenzátor s malou kapacitou dosahující řádu desetin pikofaradů). Na následujícím obrázku je principiální schéma bloku (mřížky) jednobitových paměťových buněk dynamické paměti. Ze schématu je patrné, že je každá paměťová buňka vytvořena z jednoho tranzistoru (většinou MOS s kanálem typu N) a kondenzátoru. Po přivedení logické jedničky na jeden z řádkových vodičů se všechny příslušné tranzistory v řádku matice otevřou a je možné zapisovat do paměťových buněk informace (nabíjet kondenzátory), popř. informace z buněk číst. Při čtení se kondenzátory vybijí tak, že se jejich náboj přenese do latchů (záchytných registrů tvořených většinou taktéž kondenzátorem a zesilovačem) – čtení je tedy destruktivní operací.

Blok paměťových buněk v paměti DRAM

Při použití technologie MOS a planární struktury čipů se samozřejmě nepoužívají diskrétní tranzistory ani kondenzátory, ale struktura zobrazená na následujícím obrázku. Jedná se o kolmý řez jednou paměťovou buňkou paměti DRAM, na které je patrný jak tranzistor sloužící ke čtení či zápisu dat (jeho brána je onen obdélník nahoře), tak i hluboký zářez zasahující až do substrátu čipu, který nahrazuje kondenzátor (je to mimochodem jedna z prvních vertikálních struktur, které se na čipech tvořených většinou planární technologií začaly objevovat). Vzhledem k tomu, že kapacita tohoto kondenzátoru je velmi malá a okolní prostředí není zcela nevodivé, dochází k samovolnému vybíjení kondenzátorů a tím i k postupnému přechodu z úrovně logické jedničky (pokud je bit nastavený na jedničku) do úrovně nuly, tj. k „zapomínání“ zapsané informace. Z tohoto důvodu je nutné, aby byly údaje zapsané v dynamické paměti neustále obnovovány. Obnova se provádí tak, že se naráz přečtou hodnoty všech paměťových buněk umístěných v jednom řádků a následně se tyto hodnoty zapíšou zpět.

Schematický řez paměťovou buňkou DRAM

O obnovu dat (tj. nábojů v kondenzátorech) se postarají obvody umístěné na čipu spolu s mřížkou paměťových buněk. Mikroprocesor musí udělat jedinou věc – vydat příkaz pro přečtení jedné adresy, která se nachází na paměťovém řádku, který se má obnovit (refresh), což je vlastně čtení naprázdno (způsobem adresování řádků a sloupců se budeme podrobně věnovat příště). V některých případech je obnova prováděna přirozeným způsobem (například se může jednat o grafické karty, ve kterých se postupně čte obsah obrazové paměti přenášený na displej), většinou je však obnova vynucená a poněkud zpomaluje přístup k dynamické paměti, což je jeden z důvodů vedoucích ke kombinaci dynamických pamětí s vyrovnávacími (cache) paměťmi. Postupné vybíjení jednotlivých kondenzátorů může být urychleno nárazem částice alfa (měkké záření) nebo i jiného typu částice, které způsobí ionizaci izolační vrstvy a náboj se tak vybije do substrátu čipu. To je příčinnou tzv. měkkých chyb (soft error), tj. chyb, které sice nezničí součástku, ale poškodí data uložená v DRAM. SRAM tímto problémem netrpí, u nich se měkká chyba projeví až po přijetí mnohem vyšší dávky záření.

7. Vývoj dynamických pamětí

Poměrně zajímavý je časový vývoj parametrů dynamických pamětí, který je shrnut na následujících třech obrázcích. Na prvním grafu je vynesena kapacita běžného paměťového čipu DRAM v závislosti na roku výroby. Zajímavá je především skutečnost, že na vertikální ose je logaritmické měřítko – kdyby bylo použito měřítko lineární, byl by nárůst exponenciální.

Postupný růst kapacity dynamických pamětí. Všimněte si, že na vertikální ose je logaritmické měřítko.

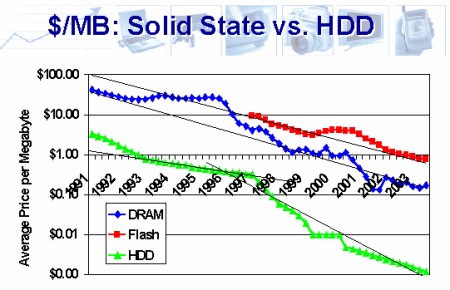

Spolu s rostoucí kapacitou paměťových čipů klesá i jejich cena přepočtená na jeden megabyte a to opět exponenciálně. Výkyvy v ceně jsou způsobeny především tím, že výrobců DRAM je poměrně malé množství (jedná se o složitou technologii) a výroba je centralizována, takže výpadek jedné jediné továrny (požár, zemětřesení atd.) se ihned projeví na celém světě. Mnozí si jistě jeden takový cenový skok pamatují.

Postupný pokles cen dynamických pamětí. Na vertikální ose je opět logaritmické měřítko.

Možná nejzajímavější je poslední graf, ve kterém jsou vyneseny některé technologické parametry dynamických pamětí. Zatímco plocha, kterou zabírá jedna paměťová buňka neustále klesá, zůstává kapacita jejího kondenzátoru přibližně stejná, což znamená, že se buď změnily vlastnosti dielektrika nebo se struktura kondenzátoru stala (při kolmém řezu) užší a současně i hlubší. Plocha celých čipů vzrostla na cca šesti až osminásobek, o čemž se ostatně můžete sami přesvědčit při porovnání čipů použitých například v osmibitových domácích počítačích (většinou se jednalo 14 vývodová pouzdra DIL, samotný čip je však menší), v prvních „krátkých“ SIMMech a pamětech použitých v dnešních počítačích. Rozdíly v kapacitách jsou však několikařádové, na rozdíl od rychlostí, které se zvyšují pouze nepatrně, většinou s pomocí některých triků popsaných příště.

Technologický vývoj dynamických pamětí. Plocha jedné buňky, plocha celého čipu a kapacita „kondenzátorů“ představujících jednotlivé bity.

8. Obsah další části seriálu

V následující části seriálu o funkci počítačů si řekneme, jakým způsobem je možné urychlit přístup do operační paměti. Lze použít jak techniky vedoucí ke zrychlení přístupu k dynamickým pamětem (FP, EDO, BEDO), tak i využít vyrovnávacích pamětí (cache) první a druhé úrovně spolu s logikou, která určuje, které informace mají být ve vyrovnávacích pamětech uchovávány.