Oddělovač portu

Port lze oddělit mnoha různými způsoby. Ochrannými odpory pro zabránění zkratu počínaje a optickým oddělením konče.

Rozumný kompromis je použít běžné logické obvody TTL (s nimiž je port kompatibilní) a získat tím de facto identický port s více zatížitelnými výstupy a odolnějšími vstupy. V případě, že se integrované obvody umístí do patic, není problém je po nějakém průšvihu velmi rychle vyměnit. Jejich ceny jsou mezi 5 a 30 Kč.

Jak funguje TTL logika

Na výstupu jsou v principu dva tranzistory mezi napájecím napětím (+Ucc) a zemí (GND) a jejich střed je vyveden jako výstup. Tyto tranzistory jsou vhodně ovládány předchozím stupněm (aby nebyly zapnuté oba najednou) a tím je dané výstupní napětí a tedy i logická úroveň. V okamžiku přepnutí je jeden částečně zapnut v době, kdy druhý není zcela vypnut, proto tyto obvody (stejně, jako CMOS) více hřejí, když něco dělají. Tento problém částečně omezuje vložená dioda. Protože všechny výstupy nejsou zcela identické, je velmi nepraktické zapojovat je paralelně. Dojde totiž k tomu, že se doba, kdy ještě nejsou uzavřeny všechny tranzistory, které se mají uzavřít, a již jsou otevřeny některé, které mají být otevřeny, výrazně prodlouží a výkonová ztráta obvodu roste. Strmost získaného signálu nemá s logikou nic společného … což ale nemusí vždy vadit – ronja toto zapojení používá a funguje – ale jedná se o štěstí nebo dlouhou sérii experimentů a zpravidla je efektivnější řešit to jinak.

Vstupy jsou z pohledu bastlíře zcela neobvyklé – jedna se totiž o emitor (emitory) tranzistoru. Rozpoznávání úrovně je proudové, nikoliv napěťové. Pokud ze vstupu teče dostatečný proud ven (do výstupu předchozího obvodu), je to 0, v opačném případě 1. Například v hradle NAND (schéma hradla NAND a popis TTL je třeba na Wikipedii) je na vstupu jeden dvouemitorový tranzistor. Tuto konstrukci vstupu je nutné mít na paměti. Je téměř jedno, co se přivede jako logická 1, ale logická 0 musí být poměrně dobrý zkrat na zem. Maximální úbytek proti zemi je 0,8 V a odpor proti zemi se většinou nedoporučuje větší, než cca 200 ohm (z náhradního schématu na Wikipedii vychází, že by to mělo chodit ještě s 600 ohm, ale je dobré nezapomínat na rušení v okolí a v napájecím napětí).

TTL logiky je několik řad. Ve stručnosti proberu ty nejdůležitější: 7400 je původní provedení. 74S00, 74LS00 a 74ALS00 mají navíc Schottkyho diody. Jsou rychlejší. 74F00 jsou nejrychlejší (přes 100MHz). 74HC00, 74HCT00 a další s písmenem C jsou realizované CMOS technologií, ale jejich vstupy a výstupy jsou kompatibilní s TTL. Také jsou rychlejší, než původní 7400. Já osobně bych raději na oddělovač použil některou z ne-CMOS variant. Měla by být odolnější a vysoká rychlost není potřeba. Nicméně máte-li doma v šuplíku jen CMOS, použijte je. Až/pokud odejdou, snadno je v paticích nahradíte jinými. I CMOS varianty řady 74 vydrží poměrně dost. Letování pistolovou páječkou není žádný problém.

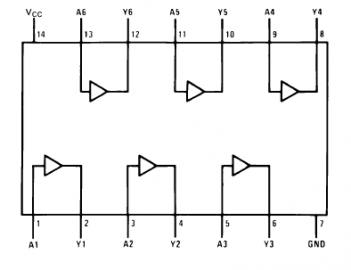

Čísla 74 znamenají řadu, je-li tam 84 nebo 54 (ani nevím, zda to vyráběl někdo jiný, než TESLA), je to stále ten samý obvod a lze ho použít. Poslední dvoj- až trojčíslí znamená typ obvodu. 00 je 4× 2-vstupový NAND, 02 4× 2-vstupový NOR, 08 4× 2-vstupový AND, 32 4× 2-vstupový OR, 04 6× invertor, 06 6× invertor s otevřeným kolektorem, 07 6× budič s otevřeným kolektorem… jsou tam i 3-vstupové, 4-vstupové a 8-vstupové logické obvody, klopné obvody a mnoho dalších.

Proč je tak oblíbené hradlo NAND

Lze z něj totiž postavit cokoliv. Spojme jeho vstupy do jednoho a máme NOT. Znegujme výstup (třeba NOT-em z druhého hradla NAND) a máme AND. Znegujme naopak oba vstupy a získáme OR, protože platí, že A OR B = NOT(NOT(A) OR (NOT(B)). Jak vznikne NOR je myslím již zřejmé a vyjma ekvivalence, non-ekvivalence (XOR) a implikace již máme všechna prakticky použitelná hradla. Koukněte se do tabulky, možná ty úpravy budou jasnější – je schválně poskládaná tak, aby to bylo dobře vidět.

NAND NOT AND OR NOR

A B | Y A | Y A B | Y A B | Y A B | Y

---------- ------- ---------- ---------- ----------

0 0 | 1 0 | 1 0 0 | 0 1 1 | 1 1 1 | 0

0 1 | 1 | 0 1 | 0 1 0 | 1 1 0 | 0

1 0 | 1 | 1 0 | 0 0 1 | 1 0 1 | 0

1 1 | 0 1 | 0 1 1 | 1 0 0 | 0 0 0 | 0 Co je otevřený kolektor

Výstup obvodu lze udělat v zásadě třemi základními způsoby. Tak, jak je nakreslen ve Wikipedii (odkaz o několik odstavců výše), tedy dva tranzistory mezi Ucc a GND, výstup mezi nimi. Ten je schopen dodat kladný i záporný proud (ze vstupu i do vstupu). Druhá možnost je tranzistor na GND, odpor na Ucc a výstup mezi nimi. Toto řešení poskytne výrazně nižší proud z výstupu a ve stavu 0 trvale odebírá proud. Třetí možnost je nechat tam jen jeden tranzistor a vyvést jeho kolektor. Pokud je třeba připojit na takový výstup další TTL obvod, stačí zapojit odpor cca 1k-4k7 proti Ucc a tím je výstup převeden na druhou variantu. Proč se to tedy používá? Má to dvě podstatné výhody. Není třeba bát se jejich paralelního spojení. Vznikne tím virtuální hradlo AND – stačí sepnout jeden jediný z těch výstupů na GND a je tam 0. Druhá výhoda je, že tranzistor lze dimenzovat na větší proud a napětí (7406 a 7407 snesou na výstupech až 30V a 40mA), takže není problém připojit na výstup logického obvodu třeba několik supersvítivých LED v sérii. Z toho také vyplývá vyšší odolnost takového výstupu.

Ted už můžeme skoro začít zapojovat… a nebo ne? Nesmíme zapomenout na blokovací kondenzátory. Ty mají být co fyzicky nejblíže k napájecím vývodům obvodu (u 14-nohých TTL 74 obvodů je vývod 7 GND a vývod 14 Ucc) a mají mít co nejmenší parazitní indukčnost. Používají se keramické typy, většinou 33nF až 100nF. Jsou tam na to, aby na chvilku – během přepnutí – pokryly výrazně zvýšenou spotřebu obvodu.

S otevřeným kolektorem, nebo bez?

Teď je nutné přijmout důležité rozhodnutí. Obvody s otevřeným kolektorem jsou odolnější, snesou větší proudy směrem do země, naopak poskytnou menší proudy při log 1 a pro připojení další logiky vyžadují pull-up odpory (odpor mezi výstupem a Ucc). Lze použít obvod 7407, případně lze znegovat již negované vstupy a výstupy, abychom získali port, kde budou všechny vstupy a výstupy fungovat stejně. Negovaných bitů je 5 (2 vstupní a 3 výstupní – viz programy v minulém dílu), přímých 12. Obvody 7407 (budiče) a 7406 (negátory) mají identické rozložení pinu (vstupy, výstupy, napájení) a v každém je 6 hradel. Takže logika velí zapojit těch 5 negovaných IO na společný obvod a zbylých 12 na dva další obvody. Pokud jsou obvody v paticích, lze záměnou jednoho obvodu předělat oddělovač z negujícího na přímý a zpět.

Pokud zvolíme zapojení s normálními výstupy, situace se poněkud zkomplikuje. Na rozdíl od negátoru (7404) totiž neexistuje šestice budičů v jednom pouzdře. Existují v řadě CMOS4000, ale dávat do oddělovače obvody CMOS není zcela praktické – méně vydrží. Pro přímé zapojení vychází nejlépe dvojice 74245 (nebo 74244, ale 74245 má na jedné straně vstupy a na druhé výstupy, kdežto 244 je má proházené). Tyto obvody jsou v pouzdře s 20 vývody a každý obsahuje 8 budičů sběrnice. Tyto budiče jsou oboustranné, takže je nutné zvolit si směr a podle toho zapojit vývod DIR (směr) a v každém případě uzemnit vývod /G (gate), jinak zůstanou všechny vývody ve třetím stavu (vysoká impedance – všechny tranzistory vypnuté). Pozorný čtenář již přišel na malou zradu – dva obvody oddělí 16 vývodů a paralelní port jich má 17. Lze to vyřešit třetím obvodem – buď stejným, nebo třeba 7400, 7404 apod., který se zapojí jako dva negátory v sérii, čímž vytvoří budič. Finanční důvody můžeme pominout (74LS245 stojí asi 9 Kč), takže bych doporučil radši použít třetí 74245, aby na všech vývodech bylo stejné zpoždění. Nicméně máte-li v šuplíku 2× 74245 a 1× 7400 a na přesném časování zpoždění vám nezáleží (při ovládání LEDek, relé a podobně), klidně je použijte. Místo 74245 by měla jít použít 74243 – je dražší, ale v menším pouzdře (14 vývodů), protože má jen 4 budiče. Pokud to budete kupovat, kupte si raději všechny stejné, až jeden shoří, bude se vám lépe nahrazovat.

Pokud chceme normální výstupy a zároveň negovat negované IO, můžeme použít 2× 74245 a 1× 7404, některá hradla opět zůstanou nevyužita.

Regulátor hlasitosti

A rozloučím se slibovanými zdrojáky regulátoru hlasitosti, který vyžaduje 3 tlačítka na paralelním portu. Konkrétně na vývodech 10, 11 a 12. První dvě mění hlasitost, třetí dělá mute. I když to není nejhezčí kus kódu (polluje port), funguje spolehlivě již několik let a spotřebovává pod 0,1 % výkonu počítače.