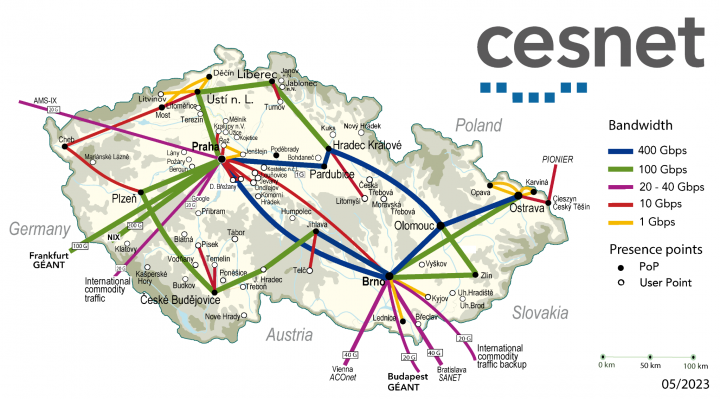

Bohužel se nedá říci, že provoz na internetu a potažmo páteřních linkách má jen neškodný charakter. Sítě jsou dnes a denně vystavovány škodlivým událostem počínaje masivními skeny veřejně vystavených zařízení, pokusy útočníků o proniknutí do zranitelných systémů a konče v poslední době stále častějšími cílenými DDoS útoky.

K tomu, abychom věděli, co se v síti odehrává, a případně na to byli schopni reagovat, potřebujeme provádět její monitorování. S tím, jak se rychlost a množství provozu stále zvyšuje, musí monitorování udržovat krok s aktuálními trendy. Právě o vývoji speciální hardwarově akcelerované sondy si povíme v tomto článku.

V rámci svých snah o inovaci a pokrok v monitorování navrhlo sdružení CESNET novou 400 GbE FPGA sondu. Na rozdíl od běžných komoditních síťových karet poskytuje technologie FPGA vysokou flexibilitu. FPGA firmware lze snadno aktualizovat, doplňovat o nové funkce nebo zcela změnit pro případnou novou aplikaci. CESNET má dlouholeté zkušenosti s vývojem firmwaru pro FPGA a návrhem vlastních FPGA karet.

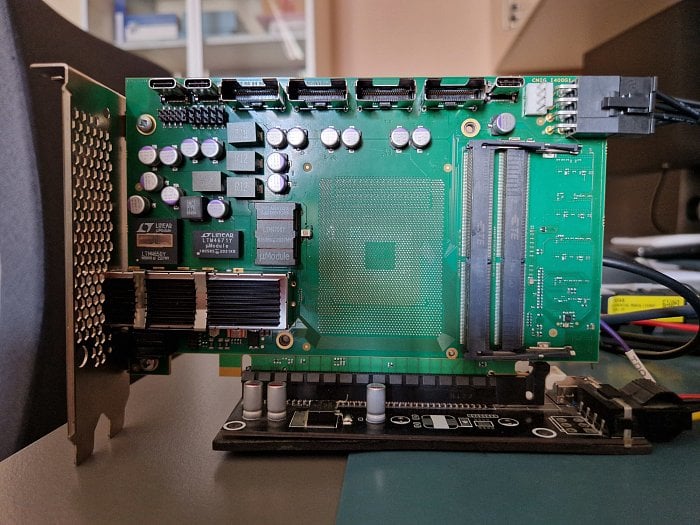

Vzhledem k technologické náročnosti výroby cílové 400 GbE FPGA karty zahájilo sdružení CESNET spolupráci s francouzskou firmou Reflex CES, která disponuje vynikajícím know-how v oblasti výroby FPGA karet. Výsledkem této spolupráce je karta s produkčním označením XpressSX AGI-FH400G.

Schopnosti této nové FPGA karty byly poprvé představeny na prestižní konferenci FPL (International Conference on Field-Programmable Logic and Applications) v roce 2022, která se konala v Belfastu. Hlavním lákadlem zde byla živá ukázka záchytu ethernetových paketů na rychlosti 400 Gb/s. Jaká byla cesta k tomuto výsledku a na čem pracujeme nyní se dočtete dále.

Vývoj 400G FPGA karty

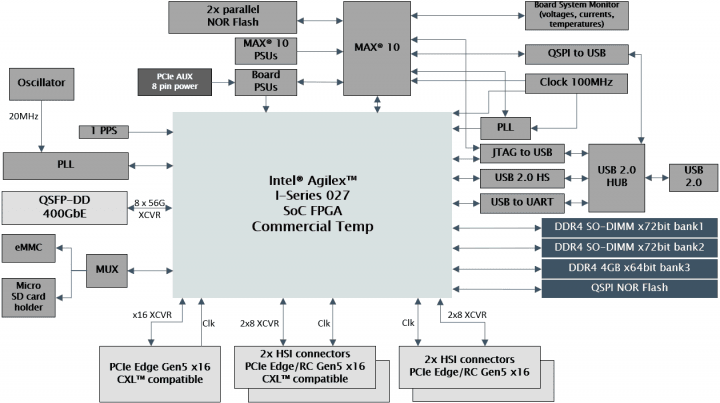

Vývoj této FPGA karty započal přibližně na začátku roku 2021. Jako cílové FPGA jsme zvolili čip z řady Intel Agilex 7 (dříve znám jako Agilex I-Series), který podporuje až 400 Gb Ethernet a PCIe rozhraní Gen5 ×16. Návrh schématu a 18vrstvého PCB (Printed Circuit Board) byl prakticky „one man show“ našeho hardwarového vývojáře Jiřího Sikory. Práce to nebyla vůbec snadná: tehdy ještě k FPGA neexistovala finální dokumentace, vše se řešilo za pochodu komunikací s Intelem a do toho všechny trápila celosvětově problematická dostupnost elektronických součástek.

Zvolené FPGA obsahuje téměř milion bloků ALM (Adaptive Logic Module), 259 Mb blokové paměti, vestavěné řadiče pro paměti DDR4, jeden blok F-Tile a tři bloky R-Tile. Tyto bloky „Tile“ implementují transceivery a řadiče pro vysokorychlostní komunikační protokoly. F-Tile přináší zejména podporu pro Ethernet (PCS + MAC + RSFEC) pro širokou škálu rychlostních standardů: od 10 GbE až po 400 GbE. Naopak R-Tile se výhradně soustředí na podporu rozhraní PCIe, které je zde k dispozici až v režimu Gen5 ×16. Ano, je to opravdu špičkově vybavený velký čip (56×45 mm) a tomu odpovídá 2957 pinů.

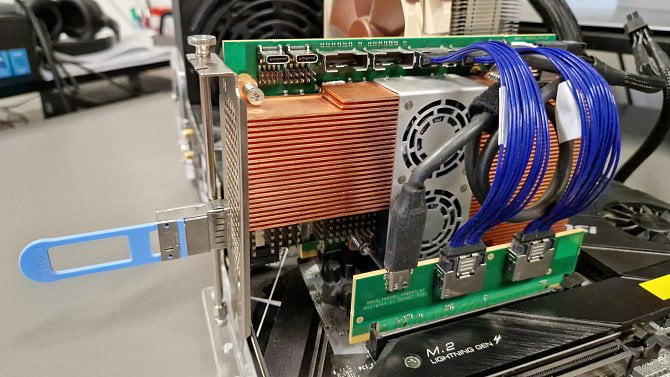

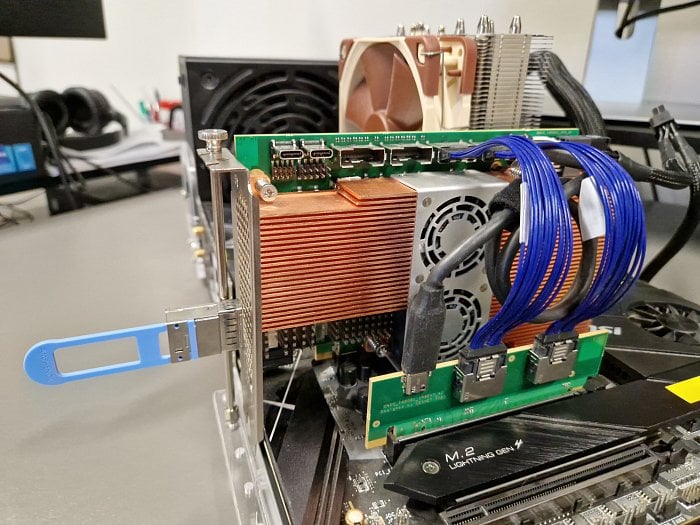

Koncem roku 2021 byl návrh karty připraven k výrobě, ale zejména kvůli neustálým problémům s dostupností součástek byl první prototyp reálně vyroben až v březnu 2022. Výrobu karty zajistil Reflex CES. Vzhledem k ceně použitého FPGA a velkému množství napájecích hladin (více než 30) začalo oživování na prototypu bez osazeného FPGA. Po jeho základním ověření následovalo oživení plně osazeného prototypu. Oživování odhalilo jen pár menších problémů (například bylo potřeba vyladit napájecí zdroje), které jsme dokázali rychle opravit.

Karta je vybavena jednou klecí QSFP-DD, která umožňuje zapojit optický transceiver (nebo alternativně kabel DAC) kompatibilní s 400 GbE. Na druhé straně je klec QSPF-DD přímo připojena k bloku F-Tile uvnitř FPGA. Pro zapojení karty do PC/serveru je zde klasický konektor PCIe ×16 s podporou až Gen5 (připojený k R-Tile), ale kdo z vás měl v roce 2022 dostupný server s podporou PCIe Gen5?

Zbylé dva bloky R-Tile poskytující další rozhraní PCIe jsou připojeny k rozšiřujícím konektorům. Díky nim je možné FPGA kartu připojit také prostřednictvím dvou konektorů PCIe Gen4 ×16 a získat tak potřebnou přenosovou rychlost 400 Gbps i přes rozhraní PCIe starší generace.

Na prvním prototypu karty jsme začali ladit FPGA firmware. K tomu jsme pro začátek použili běžné desktopové PC s CPU AMD Ryzen 3960X a FPGA kartu jsme připojili právě prostřednictvím dvou rozhraní PCIe Gen4 ×16. Pro funkční komunikaci PCIe bylo nejprve nutné odladit zapojení R-Tile PCIe Hard IP. Oproti předchozím generacím FPGA se zde změnila práce s kredity PCIe a bylo nutné se ji přizpůsobit. Na druhé straně FPGA: F-Tile Ethernet Hard IP přinesl novou segmentovou sběrnici, ke které bylo nutné připojit zbytek firmwaru. Vše se nakonec podařilo odladit a v srpnu 2022 jsme měli připravený firmware pro první demo na FPL.

Framework NDK pro FPGA

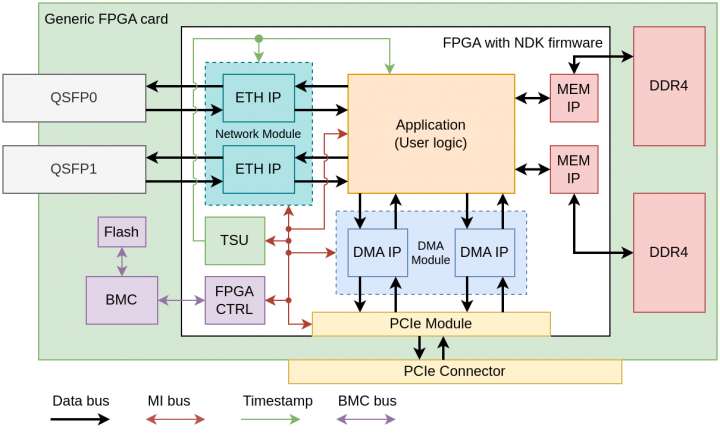

FPGA firmware použitý při živé ukázce na FPL byl postaven na open-source frameworku NDK (Network Development Kit), který sdružení CESNET vyvíjí. Framework slouží pro vývoj různých síťových aplikací pro FPGA a zdrojové kódy (VHDL) s referenční/minimální aplikací jsou dostupné na GitHubu.

Byl navržen tak, aby poskytoval prostor pro implementaci uživatelské aplikace FPGA a současně snadný přístup k rozhraním Ethernet, PCIe a k externím pamětem (typicky DDR4). Jeho součástí je také sada užitečných IP napsaných v jazyce VHDL, které často najdou uplatnění v uživatelské aplikaci. Pro ovládání firmware NDK je k dispozici linuxový ovladač, knihovna a řada užitečných ovládacích nástrojů.

Jednou z hlavních vlastností frameworku NDK je jeho modularita a možnost parametrizace, díky čemuž je možné podporovat širokou paletu různých FPGA karet s různými parametry a FPGA čipy od firmy Intel nebo od AMD/Xilinx. Takto široká podpora čipů FPGA se u podobných frameworků FPGA nevidí. Další unikátní vlastnost je podpora vyšší přenosové rychlosti než 100 Gbps, kdy už je typicky nutné umět zpracovávat více paketů v jednom hodinovém cyklu. Z toho důvodu CESNET vyvinul koncept Multi Frame/Value Bus (MFB/MVB), který je plně škálovatelný a přímo připraven na přenos a zpracování více paketů v jednom slově. S tímto běžné sběrnice typu Avalon-Stream a AXI-Stream ve svých standardech prakticky nepočítají.

V případě firmware NDK pro kartu 400GbE je datová cesta pro přenos ethernetových paketů realizována sběrnicí MFB s datovou šířkou 2048 bitů a běží na frekvenci 200 MHz. Pakety jsou na této sběrnici zarovnány po 8 bajtech. V jednom takovém datovém slově se tedy mohou objevit až čtyři nejkratší ethernetové pakety. Aby bylo možné přenést ethernetové pakety maximální rychlostí až do hostujícího PC nebo opačně, bylo nutné použít plnohodnotný 400G DMA řadič (closed-source) známý také jako DMA Medusa.

Do vývoje NDK je zapojena také řada studentů (především z VUT FIT a FEKT v Brně), kteří tak mají skvělou příležitost pracovat s nejmodernějšími FPGA kartami a jejich pracovní výsledky se reálně mohou uplatnit. Každý student, který má o tuto oblast reálný zájem, má u nás dveře vždy otevřené. Zájemci se nám mohou ozvat na cabal@cesnet.cz nebo matousek@cesnet.cz.

FPGA firmware pro monitoring

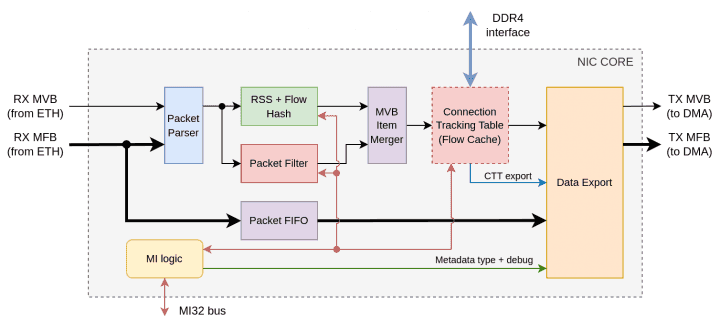

Firmware pro monitoring sítí s rychlostí až 400 GbE je rozvíjen v rámci projektu Flow-based Encrypted Traffic Analysis (FETA). Tento firmware je postaven na frameworku NDK, ale není veřejně dostupný. Aplikační jádro obsahuje několik základních modulů, které jsou znázorněny na přiloženém blokovém diagramu.

Všechny uvedené moduly dokáží zpracovávat až čtyři pakety za hodinový takt, což je potřebné pro dosažení plné 400Gbps propustnosti. Prvním modulem je paketový parser, který dokáže z každého paketu extrahovat informace z jednotlivých síťových protokolů až pro L4. Konkrétně parser podporuje následující síťové protokoly: ETH, VLAN, MPLS, IPv4/6, IPv6_EXT, TCP, UDP, ICMP a SCTP.

Následující modul RSS slouží ke směrování paketů na jednotlivé fronty DMA dle vypočtené haše. Modul je plně konfigurovatelný: lze zvolit hašovací funkci, 40B klíč a informace pro vstupní vektor, ze kterého se haš počítá. Součástí modulu RSS je i konfigurovatelná RETA tabulka.

K dispozici je také modul pro základní filtraci paketů podle nastavených pravidel. Paketový filtr využívá jednoduchou paměť TCAM. Filtrovat pakety lze podle IP adres, čísla protokolu L4, portů, VLAN TCI a dalších základních položek z hlaviček paketů.

Tohle všechno jsou v zásadě jen základní funkce běžné síťovky vyladěné k podpoře 400 GbE. Flexibilita FPGA nám však umožňuje postupně funkcionalitu rozšiřovat. V dalších verzích plánujeme doplnit Connection Tracking Tabulku (CTT) napojenou na externí paměť, která nám umožní akcelerovat výpočet a udržovat statistiky jednotlivých síťových toků přímo v FPGA. Do budoucna se také plánuje integrace se systémem Suricata nebo podpora dešifrování novějšího protokolu QUIC přímo v FPGA.

Modul DataExport umožňuje zahodit nebo ořezat vybrané pakety. Před odesláním paketu do DMA (respektive do paměti PC) k němu připojí také získaná metadata (například časovou značku, informace o získaných protokolech apod.). Mimo to je modul DataExport připraven odesílat také exportované záznamy z CTT.

Konfiguraci celého firmwaru zajišťuje sada nástrojů a skriptů. Síťové pakety a metadata odeslaná do software zpracovává open-source nástroj ipfixprobe. Monitorovací infrastruktura sdružení CESNET již nyní používá obdobný 100GbE firmware se staršími FPGA kartami. Výše popsané řešení přináší podporu novějších FPGA karet a možnost monitoringu také na nových až 400Gb páteřních sítí.

(Autorem obrázků jsou zaměstnanci organizace CESNET.)