Obsah

1. Zásobníkové procesory jako alternativa k architekturám CISC a RISC?

2. Limity klasické architektury RISC

3. Velikost programového kódu a využití vyrovnávacích pamětí

4. Volání subrutin, podmíněné skoky, reakce na přerušení a přepínání kontextu

6. Instrukční sada zásobníkových procesorů

7. Příklad „horizontální“ instrukční sady zásobníkového procesoru HARRIS RTX 2000

8. Instrukce ALU aneb až čtyři operace zapsané do 16bitového instrukčního slova

1. Zásobníkové procesory jako alternativa k architekturám CISC a RISC?

Mikroprocesory s redukovanou instrukční sadou (RISC), jejichž popisem jsme se zabývali v předcházejících sedmi částech seriálu o architekturách počítačů, jsou založeny na myšlence zpracování instrukcí s využitím většinou čtyřfázové popř. pětifázové instrukční pipeline, v níž se instrukce rozkládají na několik jednodušších podoperací, přičemž každá tato podoperace může být vykonána v jiném funkčním bloku procesoru (některé RISCové procesory ovšem používají i instrukční pipeline s více fázemi, například třinácti u mikroprocesorů ARM Cortex-A8). Díky existenci instrukční pipeline je možné za ideálních podmínek v každém strojovém taktu začít zpracovávat novou instrukci a navíc mohou být strojové cykly u většiny RISCových procesorů zkráceny, tj. může být zvýšena frekvence hodinových pulsů, protože komunikace mezi prostorově vzdálenými funkčními bloky je omezena. Konstruktéři procesorů RISC byli přesvědčeni, že se jim podařilo vytvořit takovou architekturu procesorů, která dokáže při dané úrovni technologie přinést nejvyšší výpočetní výkon, což je ostatně pravda, protože například čip SPARC64 VIIIfx „Venus“ patří mezi nejvýkonnější procesory současnosti.

Obrázek 1: Jeden z nejvýkonnějších procesorů současnosti – SPARC64 VIIIfx (kódové jméno „Venus“) s osmi jádry a špičkovým výkonem dosahujícím 128 GFLOPS.

I přes některé technologické rozdíly můžeme u všech tří nejvýznamnějších rodin RISCových mikroprocesorů (MIPS, SPARC, PA-RISC a částečně i u procesorů ARM) najít některé společné vlastnosti. Patří mezi ně například relativně velký počet pracovních registrů (většinou se jedná o registrová okna s 32 v dané chvíli viditelnými pracovními registry), „tříadresová“ instrukční sada s aritmetickými a logickými instrukcemi, jejichž operandy tvoří trojice pracovních registrů, popř. dvojice registrů a konstanta, pevná délka instrukcí zarovnaných na 32 bitů, existence registru obsahujícího konstantní hodnotu nula (nikoli u všech procesorů ARM) a společné mají tyto procesory taktéž způsob volání subrutin, kdy se pro uložení návratové adresy využívá jeden z pracovních registrů nazývaný z tohoto důvodu link register. Přednosti architektury RISC se tedy projeví především při použití překladačů, které dokážou možnosti těchto procesorů co nejlépe využít, aby například nedocházelo k nucenému čekání na dokončení předchozí instrukce (typickým příkladem může být operace porovnání/rozdílu dvou operandů následovaná podmíněným skokem, popř. dvojice instrukcí pracujících s registrem, jehož hodnota je první instrukcí modifikována).

Obrázek 2: Maska použitá při výrobě mikroprocesoru RISC I.

Zdroj: C.E. Sequin and D.A.Patterson: Design and Implementation of RISC I

2. Limity klasické architektury RISC

První funkční vzorky mikroprocesorů s architekturou RISC vznikly již na počátku osmdesátých let minulého století a prakticky ihned vzbudily mezi odbornou veřejností velký zájem, protože se jednalo o mikroprocesory s relativně malým množstvím tranzistorů (takže i poměrně levné), ale zato s velkým výpočetním výkonem – ostatně sám David Andrew Patterson, který stál u vzniku architektury RISC vzpomíná, jak vzrušující bylo zkonstruovat spolu s několika studenty skutečně pracující procesor, který dokázal svou rychlostí překonat v té době kralující procesory CISC vyvinuté bohatými společnostmi, jakými byly Intel, Motorola či HP. Zhruba v polovině osmdesátých let pak nastala pravá „revoluce RISC“, protože se mikroprocesory s touto architekturou staly součástí pracovních unixových stanic, výkonných serverů, grafických akcelerátorů firmy SGI a později též součástí různých vestavných zařízení – odhaduje se, že v současnosti mají v této oblasti přibližně devadesátiprocentní zastoupení čipy ARM následované čipy MIPS.

Obrázek 3: Mikroprocesor HP PA-RISC 7300LC (PA=Precision Architecture). Jedná se moderní variantu procesorů RISC se zabudovaným matematickým koprocesorem a sadou 32bitových celočíselných registrů a taktéž 64bitových registrů pro FPU operace.

Zdroj: Wikipedia

Ovšem v oboru IT (a nejenom zde) platí, že neexistuje žádná stříbrná kulka, přesněji řečeno technologie, která by elegantně vyřešila všechny problémy. I když se okolo roku 1985 zdálo, že procesory RISC předčí všechny další typy mikroprocesorů, ukázalo se později, že klasická architektura RISC má i své limity a proto není její použití v některých oblastech ideální. První limit vychází z pevné délky instrukcí. Aritmetické a logické instrukce musí mít ve svém instrukčním slovu uloženy adresy obou operandů i adresu cíle operace (viz již zmíněný tříadresový kód), nebo i konstantu používanou jako jeden z operandů, popř. jako relativní adresu skoku. Kvůli těmto požadavkům se u klasické architektury RISC používají instrukce s pevnou délkou 32 bitů. Ovšem právě zde leží zmíněný problém limitující výpočetní výkon – pokud se každá instrukce provede v ideálním případě v jednom taktu, musí se také v každém taktu načíst instrukce nová, tj. celých 32 bitů; a to navíc nepočítáme s tím, že se může jednat o instrukci typu Load či Store, která přistupuje k operační paměti za účelem čtení či zápisu obsahu jednoho pracovního registru.

Obrázek 4: Osobní počítač firmy Acorn, který byl vybavený mikroprocesorem s architekturou RISC.

3. Velikost programového kódu a využití vyrovnávacích pamětí

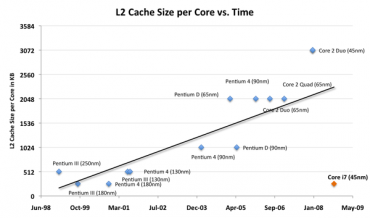

Tento limit klasické architektury RISC obešli konstruktéři mikroprocesorů zdánlivě jednoduše – použitím vyrovnávacích pamětí (cache). V některých případech tvořily (a doposud tvoří) vyrovnávací paměti hierarchii, protože přímo na čipu byla umístěna rychlá vyrovnávací paměť první úrovně (cache level 1 – L1) a většinou mimo procesorový čip pak vyrovnávací paměť druhé úrovně (cache level 2 – L2). Ovšem spolu s rostoucím výpočetním výkonem mikroprocesorů a nepřímo úměrně klesající délkou strojového cyklu se každý výpadek vyrovnávací paměti (cache miss) citelně projevil na reálném výpočetním výkonu. Situace se samozřejmě ještě zhoršuje při použití multitaskingu, protože se kvůli přepínání úloh zhoršuje lokalita instrukcí i lokalita dat. Z tohoto důvodu používají (nejenom) procesory s architekturou RISC mnohdy velmi sofistikované způsoby, jak zajistit co největší poměr mezi cache hit a cache miss a kapacity vyrovnávacích pamětí taktéž postupně rostou, i když ne stejným tempem, jako kapacity operačních pamětí.

Obrázek 5: Server s architekturou Onyx 350.

Taktéž celková délka programů je u klasické architektury RISC většinou delší, než je tomu u architektury CISC, což sice většinou nepůsobí větší problémy při použití těchto mikroprocesorů v pracovních stanicích a serverech (kde je většinou limitujícím faktorem spíše množství dat), ovšem v segmentu vestavných zařízení (například s jádry RISC použitými v mikrořadičích) je již situace poněkud odlišná, protože se jedná o segment velmi citlivý na cenový rozdíl mezi mikrořadiči s rozdílnou kapacitou paměti programu. Výrobci procesorů RISC jsou si tohoto problému samozřejmě vědomi, proto je například u rodiny ARM s instrukčními sadami Thumb a Thumb-2 klasická architektura RISC poněkud upravena takovým způsobem, že se namísto 32bitových instrukcí používají instrukce 16bitové, v nichž jsou některé operandy určeny implicitně a některé kombinace operandů dokonce vůbec není možné použít. Za kratší velikost programového kódu tedy programátoři platí poněkud omezenějším repertoárem instrukcí a nepatrně složitějším/dražším procesorem (ovšem naprostá většina vývojářů je od assembleru a strojového kódu stejně izolována díky překladačům vyšších programovacích jazyků).

Obrázek 6: Mikroskopický pohled na část čipu R2000.

4. Volání subrutin, podmíněné skoky, reakce na přerušení a přepínání kontextu

Další oblastí, v níž se projevuje určitý nedostatek architektury RISC, je volání subrutin, provádění podmíněných skoků, reakce na přerušení a přepínání kontextů, například přepnutí do jiného vlákna nebo dokonce do jiného procesu. Ve všech těchto případech totiž procesor musí vyprázdnit instrukční pipeline a tím pádem přerušit nebo dokončit již rozpracované operace, což může být problematické u těch procesorů, které mají v pipeline vytvořeny „zkratky“ pro zpětné kopírování výsledků aritmetických a logických operací (ostatně zkuste se sami zamyslet nad tím, jak se tento problém řeší v případě, že došlo k programové změně registru PC). U podmíněných skoků znamená vyprázdnění pipeline zpomalení o několik strojových cyklů, což se moderní procesory s architekturou RISC snaží eliminovat využitím již popsaných branch delay slotů (instrukce či více instrukcí uložených ihned po instrukci podmíněného skoku jsou vždy provedeny nezávisle na výsledku vyhodnocení podmínky), prediktorů skoků i dalšími triky. Uvádí se, že při použití branch delay slotů je možné ihned za instrukci skoku v až 70% případů umístit smysluplnou instrukci, jen ve zbývajících 30% se musela použít pseudoinstrukce NOP, například „prázdný“ součet typu ADD Rd, R0, R0.

Obrázek 7: Postupný růst velikosti vyrovnávacích pamětí druhé úrovně u architektury x86.

V některých případech je však mnohem horší zpoždění vznikající při reakci procesoru na přerušení, tj. časový interval mezi přijetím přerušovacího signálu a zavoláním přerušovací rutiny. I zde se musí vyprázdnit instrukční pipeline, navíc je ovšem nutné pro přerušovací rutinu připravit novou sadu pracovních registrů takovým způsobem, aby se při ukončení přerušovací rutiny mohlo řízení vrátit původnímu procesu. Výrobci mikroprocesorů RISC tuto problematiku řeší především využitím registrových oken, použitím záložní sady pracovních registrů, popř. – například u procesorů ARM Cortex-M3 – i tím, že pracovní registry jsou ve skutečnosti uloženy na zásobníku, což je ovšem technologie v podstatě velmi podobná technologii registrových oken. Ovšem využití těchto technik vede k větší složitosti procesorů, což může být kritické například u mikrořadičů založených na architektuře RISC (na tomto místě je však vhodné poznamenat, že u procesorů CISC bývá reakce na příchod přerušení ještě pomalejší, a to zejména tehdy, pokud je prováděna nějaká složitá instrukce trvající delší počet strojových cyklů).

Obrázek 8: Chuck Moore jenž je tvůrcem jazyka Forth, který je založen na využití dvojice zásobníků (zásobníku operandů a zásobníku návratových adres).

5. Zásobníkové procesory

Zajímavou i když dnes již málo využívanou alternativou k procesorům s architekturou CISC a současně i k procesorům s architekturou RISC jsou takzvané zásobníkové procesory (stack processors). Tyto typy procesorů, jejichž princip byl mimochodem použit i u některých mainframů a minipočítačů, jsou většinou založeny na dvojici zásobníků (stack, LIFO – Last In First Out), přičemž prvním z těchto zásobníků je zásobník operandů (použitý však taktéž pro předávání parametrů volaným subrutinám), druhým zásobníkem je zásobník návratových adres. Procesory s touto architekturou jsou v naprosté většině případů jednodušší, než typičtí představitelé procesorů CISC a mnohdy jsou taktéž jednodušší, než procesory s architekturou RISC, což je způsobeno několika skutečnostmi. Jedním z důvodů je odlišný formát instrukcí u některých zásobníkových procesorů, které mohou díky absenci adres operandů (viz další kapitolu) využívat takzvané horizontální kódování, které se v mnoha ohledech podobá kódům použitým u mikroinstrukcí (viz též části tohoto seriálu věnované mikroprocesorům vybaveným mikrořadičem).

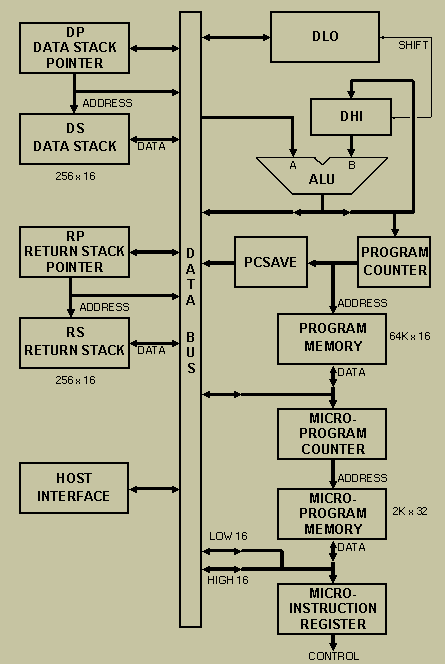

Obrázek 9: Blokové schéma procesoru WISC CPU/16.

Zdroj: Philip Koopman – Architecture of the WISC CPU/16

Další zjednodušení zásobníkových procesorů vyplývá z toho, že veškeré operace jsou prováděny s dvojicí či trojicí operandů uložených na vrcholu zásobníku, přičemž samotný procesor má několik prvních prvků zásobníku umístěnou v lokálních registrech (může se jednat například o šestnáct prvků, v některých případech však o pouze dva či tři nejvyšší prvky). Ovšem i šestnáct prvků – lokálních registrů – zabírá mnohem menší plochu čipu než například dvanáct překrývajících se registrových oken po 32 pracovních registrech. Zásobníkové procesory se vyznačují i další zajímavou vlastností, například tím, že se u nich počet fází pipeline většinou zmenšuje pouze na dvě fáze (operace). U mnohých zásobníkových procesorů se tedy „klasická RISCová“ pipeline vůbec nepoužívá, což sice znamená, že procesor nedokáže v každém taktu dokončit jednu instrukci, na druhou stranu však instrukce u mnoha zásobníkových procesorů bývají poměrně komplikované, protože se současně provádí větší množství operací.

Obrázek 10: Moduly procesoru WISC CPU/16, v nichž je implementován mikroprogramový řadič.

Poznámka: pokud vás zajímá, jak je možné u zásobníkových procesorů zkrátit jejich instrukční pipeline na pouhé dvě fáze, vyčkejte na následující část tohoto seriálu.

6. Instrukční sada zásobníkových procesorů

Již v předchozí kapitole jsme si naznačili, že se zásobníkové procesory liší od architektury CISC i RISC mj. i v použitém formátu instrukcí. Skutečně je tomu tak, protože většina procesorů CISC a všechny procesory RISC mají instrukční sadu, v níž se nachází instrukce pracující s obsahem pracovních registrů, popř. přímo s obsahem nějakým způsobem adresovaných paměťových buněk. Jedná se především o aritmetické a logické instrukce, u nichž je nutné přímo v instrukčním slově rezervovat dostatečný počet bitů na uložení adres operandů – u pracovních registrů se jedná o jejich indexy, v případě použití adresových buněk o absolutní či relativní adresy těchto buněk. Zatímco u procesorů typu RISC se většinou pro aritmetické a logické operace používají pouze pracovní registry, mohou být u procesorů typu CISC použity mnohdy velmi složité (ale i výkonné) adresovací režimy, například ve stylu LEA ECX, [EBX + 4*EAX + offset]. U obou architektur, tj. jak RISC, tak i CISC, se tedy nikoli nezanedbatelná část instrukčního slova musí „obětovat“ pro specifikaci operandů. Pod tímto odstavcem je pro ilustraci ukázán formát instrukcí RISCových procesorů MIPS:

I-Type (immediate) ------------------------------------------------------------ | 31 26 | 25 21 | 20 16 | 15 0 | ------------------------------------------------------------ | opcode (6) | rs (5) | rt (5) | offset/konstanta (16) | ------------------------------------------------------------ J-Type (jump) ------------------------------------------------------------ | 31 26 | 25 0 | ------------------------------------------------------------ | opcode (6) | adresa (26) | ------------------------------------------------------------ R-Type (register) ------------------------------------------------------------ | 31 26 | 25 21 | 20 16 | 15 11 | 10 6 | 5 0 | ------------------------------------------------------------ | opcode (6) | rs (5) | rt (5) | rd (5) | shift | operace | ------------------------------------------------------------

Obrázek 11: Subsystém zásobníku operandů (zvýrazněno modrou barvou) a zásobníku návratových adres (zvýrazněno barvou červenou).

Ovšem zcela opačná situace panuje u některých mikroprocesorů majících pouze jeden či dva pracovní registry – akumulátory (například se jedná o slavné osmibitové mikroprocesory Motorola 6800 a MOS 6502) a taktéž u zásobníkových procesorů. U zásobníkových procesorů se pro adresaci operandů aritmetických a logických instrukcí ve skutečnosti mnohdy nemusí „obětovat“ ani jeden bit, protože již z kódu prováděné operace je zřejmé, kolik operandů bude přečteno ze zásobníku (a implicitně se vždy předpokládá, že se bude jednat o operandy umístěné na jeho vrcholu, popř. těsně pod vrcholem). To znamená, že instrukční kódy bývají u zásobníkových procesorů buď velmi krátké (což je případ procesoru F21, kde je každá instrukce uložena pouze v pěti bitech!, vždy čtveřice instrukcí se sdružuje do 20bitového slova), nebo se naopak používá relativně dlouhý instrukční kód (16 bitů či 32 bitů), ovšem prakticky všechny bity jsou v těchto instrukcích použity pro uložení příkazů pro aritmeticko-logickou jednotku, popř. pro adresovací jednotku a jednotky určené pro zvýšení/snížení ukazatelů na vrchol zásobníků.

Obrázek 12: Formát mikroinstrukčního slova procesoru WISC CPU/16, na němž je patrné rozdělení mikroinstrukce na několik samostatných bloků. Adresa další mikroinstrukce je získána na základě obsahu bitů 23, 24 a 25.

Zdroj: Philip Koopman – Architecture of the WISC CPU/16

7. Příklad „horizontální“ instrukční sady zásobníkového procesoru HARRIS RTX 2000

V této kapitole je pro ilustraci ukázána základní struktura instrukční sady zásobníkového mikroprocesoru RTX 2000 navrženého a vyráběného firmou Harris Semiconductor. Instrukce mají pevnou délku šestnáct bitů a mohou být rozděleny do pěti skupin na základě struktury bitových polí, z nichž se každé 16bitové slovo skládá. Nejjednodušší a současně i velmi často používanou instrukcí je instrukce pro volání podprogramu (subrutiny). Tato instrukce obsahuje 15bitovou adresu subrutiny (nejvyšší bit je vždy nulový pro odlišení od ostatních typů instrukcí), ovšem díky zarovnání všech instrukcí na 16 bitů je rozsah paměti programu (nikoli paměti dat!) omezen na 64kB. Procesor však taktéž obsahuje stránkovací jednotku a i zásobník návratových adres má šířku 21 bitů, což znamená, že skutečná kapacita paměti programu je větší, než zmíněných 64kB (konkrétní velikost paměti programu záleží na způsobu zapojení mikroprocesoru). Instrukce pro volání podprogramu má následující tvar (parametry se samozřejmě předávají přes zásobník operandů):

--------------------------------------------------------------------------------- | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | --------------------------------------------------------------------------------- | 0 | adresa podprogramu ležící v rozsahu 0..32767 | ---------------------------------------------------------------------------------

Obrázek 13: Blokové schéma mikroprocesoru HARRIS RTX 2000. Povšimněte si, že jedním operandem vstupujícím do aritmeticko-logické jednotky je vždy interní registr TOP nesoucí hodnotu prvku uloženou na vrcholu zásobníku. Díky tomu částečně odpadá dekódování instrukce a příprava operandů na vstup do ALU, už jen z toho důvodu, že interní sběrnice YBUS (pravá část schématu) nikdy není blokována nutností přenosu dvou operandů), protože se případný přenos do interního registru TOP provádí přes samostatnou sběrnici TBUS. Podobná struktura se používá i u některých dalších zásobníkových procesorů, naproti tomu první generace mikroprocesorů s architekturou CISC byla vybavena jedinou datovou interní sběrnicí, která se částečně stala úzkým hrdlem procesoru.

Autor: Philip Koopman

Dalším typem instrukcí jsou instrukce pro provedení podmíněného skoku. K dispozici jsou čtyři typy skoků – skok provedený v případě, že je prvek uložený na vrcholu zásobníku roven nule s odstraněním tohoto prvku, stejný skok, ovšem s jeho odstraněním vždy (bez ohledu na podmínku), nepodmíněný relativní skok a skok v případě, že je hodnota speciálního registru INDEX rovna nule (před vyhodnocením podmínky se navíc hodnota tohoto registru automaticky sníží o jedničku, proto se tento typ skoku používá pro implementaci počítaných smyček). Adresa skoku je specifikována devítibitovou adresou přičítanou buď k aktuální paměťové stránce, předchozí stránce, následující stránce nebo stránce číslo 0, v níž jsou většinou umístěny často používané nízkoúrovňové rutiny operačního systému:

---------------------------------------------------------------------------------

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

---------------------------------------------------------------------------------

| 1 | 0 | 0 |podmínka | stránka | adresa cíle podmíněného skoku |

---------------------------------------------------------------------------------

podmínka: 00 - skok při T==0, DROP T

01 - DROP T, skok při T==0

10 - nepodmíněný skok

11 - INDEX--, skok při INDEX==0

Obrázek 14: Slavný kalkulátor HP-35 s RPN (převrácenou Polskou notací) založenou na zásobníku operandů

(35 v názvu tohoto přístroje značí počet tlačítek).

8. Instrukce ALU aneb až čtyři operace zapsané do 16bitového instrukčního slova

Instrukční sada mikroprocesoru RTX 2000 je odvozena od instrukčních sad používaných na starších procesorech Novix NC4016 a MISC M17 a má s těmito předchůdci mnoho společných vlastností, například to, že instrukce mohou v instrukčním kódu obsahovat větší množství operací. Z tohoto důvodu se v technické dokumentaci k zásobníkovým mikroprocesorům většinou nevypisují všechny možné kombinace operací uložených v jedné instrukci, ale pouze instrukční formát. Slučování více operací do jedné instrukce je úkol překladače, podobně jako je tomu u architektury RISC při alokaci pracovních registrů, eliminaci neužitečných branch delay slotů atd. Tento přístup je názorně demonstrován na instrukcích pracujících s aritmeticko-logickou jednotkou, jejichž formát je následující:

--------------------------------------------------------------------------------- | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | --------------------------------------------------------------------------------- | 1 | 0 | 1 | 0 | výběr operace ALU | inv| -- |ret | 0 | výběr op.shifteru | ---------------------------------------------------------------------------------

Obrázek 15: Zásobníkový mikroprocesor SEAforth-24 optimalizovaný, jak již jeho název napovídá, pro běh programů naprogramovaných ve Forthu.

Právě na instrukčním formátu vypsaném výše je názorně vidět, jak je možné do relativně krátkého šestnáctibitového instrukčního slova vložit příkazy pro provedení hned několika operací. Ve čtyřech bitech instrukčního slova je ve čtyřech bitech specifikována operace prováděná pomocí aritmeticko-logické jednotky:

0000 T (kopie T) 0001 - 0010 T and Y 0011 T nor Y 0100 Y - T 0101 Y - T - borrow 0110 T or Y 0111 T nand Y 1000 T + Y 1001 T + Y + carry 1010 T xor Y 1011 T xnor Y 1100 T - Y 1101 T - Y - borrow 1110 - 1111 Y (kopie Y)

V sedmém bitu je specifikováno, že se výsledek ALU operace má navíc invertovat, což je vlastně operace prováděná „zadarmo“ přímo v aritmeticko-logické jednotce. Zajímavý je pátý bit, který lze použít pro návrat ze subrutiny současně s prováděním ALU operace; opět se tedy jedná o funkci prováděnou bez jakéhokoli zdržování běhu programu (proto se také někdy s nadsázkou říká, že zásobníkové procesory dokážou provést návrat ze subrutiny v nula strojových cyklech). První čtyři bity určují, jaká operace je prováděna ve shifteru s výsledkem vypočteným v aritmeticko-logické jednotce:

0000 žádná operace (kopie výsledku) 0001 0 (vynulování) 0010 posun doleva 0011 posun doleva s přenosem 0100 logický posun doprava s přenosem 0101 aritmetický posun doprava s přenosem 0110 logický posun doprava 0111 aritmetický posun doprava 1000-1111 32bitové posuny

Překladač tedy v ideálním případě dokáže do jediného šestnáctibitového slova zapsat čtveřici operací, například součet následovaný inverzí výsledku následovaný aritmetickým posunem doprava a navíc se v průběhu těchto operací (tj. paralelně s výpočtem) provede návrat ze subrutiny. Pokud by se stejná sekvence operací prováděla na některém již popsaném RISCovém procesoru, bylo by ji nutné zakódovat do čtveřice 32bitových slov, což znamená, že zásobníkový procesor je v tomto (nutno opět podotknout, že značně ideálním) případě 8× efektivnější, pokud bereme v úvahu kapacitu obsazené paměti programu.

Obrázek 16: Jeden z prvních kalkulátorů s RPN (převrácenou Polskou notací) od firmy HP (HP 9810).

9. Odkazy na Internetu

- Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - Philip Koopman: Stack Computers: the new wave

http://www.ece.cmu.edu/~koopman/stack_computers/contents.html - Hewlett Packard PA-8800 RISC (LOSTCIRCUITS)

http://www.lostcircuits.com/mambo//index.php?option=com_content&task=view&id=42&Itemid=42 - PA-RISC 1.1 Architecture and Instruction Set Reference Manual

http://h21007.www2.hp.com/portal/download/files/unprot/parisc/pa1–1/acd.pdf - Fotografie mikroprocesorů HP PA (stránka 1)

http://www.chipdb.org/cat-pa-risc-592.htm - Fotografie mikroprocesorů HP PA (stránka 2)

http://www.chipdb.org/cat-pa-risc-592.htm?page=2 - Fotografie mikroprocesorů HP PA (stránka 2)

http://www.chipdb.org/cat-pa-risc-592.htm?page=3 - PA-RISC (Wikipedia)

http://en.wikipedia.org/wiki/PA-RISC - The Great CPU List: Part VI: Hewlett-Packard PA-RISC, a conservative RISC (Oct 1986)

http://jbayko.sasktelwebsite.net/cpu4.html - HP 9000/500 FOCUS

http://www.openpa.net/systems/hp-9000_520.html - HP FOCUS Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/HP_FOCUS - HP 3000 (Wikipedia)

http://en.wikipedia.org/wiki/HP_3000 - The SPARC Architecture Manual Version 8 (manuál v PDF formátu)

http://www.sparc.org/standards/V8.pdf - The SPARC Architecture Manual Version 9 (manuál v PDF formátu)

http://developers.sun.com/solaris/articles/sparcv9.pdf - SPARC Pipelining

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/pipelining.html - SPARC Instruction

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - OpenSPARC

http://www.opensparc.net/ - History of SPARC systems 1987 to 2010

http://www.sparcproductdirectory.com/history.html - Sun-1 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-1 - Sun-2 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-2 - Sun-3 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-3 - Sun386i (Wikipedia)

http://en.wikipedia.org/wiki/Sun386i - Sun 386i/250

http://sites.inka.de/pcde/site/sun386i.html - SPARC Instruction Set

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - MIPS Architecture Overview

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/mips.html - MIPS Technologies R3000

http://www.cpu-world.com/CPUs/R3000/ - CPU-collection: IDT R3010 FPU

http://www.cpu-collection.de/?tn=0&l0=co&l1=IDT&l2=R3010+FPU - The MIPS R2000 Instruction Set

http://suraj.lums.edu.pk/~cs423a05/Reference/MIPSCodeTable.pdf - Maska mikroprocesoru RISC 1

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC1.jpg - Maska mikroprocesoru RISC 2

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC2.jpg - The MIPS Register Usage Conventions

http://pages.cs.wisc.edu/~cs354–2/beyond354/conventions.html - C.E. Sequin and D.A.Patterson: Design and Implementation of RISC I

http://www.eecs.berkeley.edu/Pubs/TechRpts/1982/CSD-82–106.pdf - Berkeley RISC

http://en.wikipedia.org/wiki/Berkeley_RISC - Great moments in microprocessor history

http://www.ibm.com/developerworks/library/pa-microhist.html - Microprogram-Based Processors

http://research.microsoft.com/en-us/um/people/gbell/Computer_Structures_Principles_and_Examples/csp0167.htm - A Brief History of Microprogramming

http://www.cs.clemson.edu/~mark/uprog.html - Architecture of the WISC CPU/16

http://www.ece.cmu.edu/~koopman/stack_computers/sec4_2.html - Zásobníkový procesor WISC CPU/16 (Root.CZ)

http://www.root.cz/clanky/programovaci-jazyk-forth-a-zasobnikove-procesory-16/#k03 - Writable instruction set, stack oriented computers: The WISC Concept

http://www.ece.cmu.edu/~koopman/forth/rochester87.pdf - The Great CPU List: Part X: Hitachi 6301 – Small and microcoded (1983)

http://jbayko.sasktelwebsite.net/cpu2.html#Sec2Part10 - What is RISC?

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/whatis/ - RISC vs. CISC

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/risccisc/ - RISC and CISC definitions:

http://www.cpushack.com/CPU/cpuAppendA.html - The Evolution of RISC

http://www.ibm.com/developerworks/library/pa-microhist.html#sidebar1 - SPARC Processor Family Photo

http://thenetworkisthecomputer.com/site/?p=243 - SPARC: Decades of Continuous Technical Innovation

http://blogs.oracle.com/ontherecord/entry/sparc_decades_of_continuous_technical - The SPARC processors

http://www.top500.org/2007_overview_recent_supercomputers/sparc_processors - Maurice V. Wilkes Home Page

http://www.cl.cam.ac.uk/archive/mvw1/ - Papers by M. V. Wilkes (důležitá je především jeho práce číslo 35)

http://www.cl.cam.ac.uk/archive/mvw1/list-of-papers.txt - Microprogram Memory

http://free-books-online.org/computers/advanced-computer-architecture/microprogram-memory/ - First Draft of a report on the EDVAC

http://qss.stanford.edu/~godfrey/vonNeumann/vnedvac.pdf - Introduction to Microcontrollers

http://www.pic24micro.com/cisc_vs_risc.html - Reduced instruction set computing (Wikipedia)

http://en.wikipedia.org/wiki/Reduced_instruction_set_computer - MIPS architecture (Wikipedia)

http://en.wikipedia.org/wiki/MIPS_architecture - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - Classic RISC pipeline (Wikipedia)

http://en.wikipedia.org/wiki/Classic_RISC_pipeline - R2000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R2000_(microprocessor) - R3000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R3000 - R4400 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R4400 - R8000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R8000 - R10000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R10000 - SPARC (Wikipedia)

http://en.wikipedia.org/wiki/Sparc - SPARC Tagged Data – otázka

http://compilers.iecc.com/comparch/article/91–04–079 - SPARC Tagged Data – odpověď #1

http://compilers.iecc.com/comparch/article/91–04–082 - SPARC Tagged Data – odpověď #2

http://compilers.iecc.com/comparch/article/91–04–088 - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Microcode (Wikipedia)

http://en.wikipedia.org/wiki/Microcode - Microsequencer (Wikipedia)

http://en.wikipedia.org/wiki/Microsequencer - Maurice Wilkes (Wikipedia)

http://en.wikipedia.org/wiki/Maurice_Wilkes - Micro-operation (Wikipedia)

http://en.wikipedia.org/wiki/Micro-operation