Obsah

1. Různé varianty PCI sběrnic

2. Tvary konektorů PCI sběrnic

3. Komunikace procesoru a zařízení připojených na PCI sběrnici

4. Přenos dat přes mailboxy čipu AMCC S5933/S5935

5. Přenosové operace typu Pass Thru (do paměti mapované regiony)

6. Blokové přenosy dat

7. Bus-master přenos

8. Literatura a odkazy na Internetu

9. Obsah následující části seriálu

1. Různé varianty PCI sběrnic

V předchozí části tohoto seriálu byly uvedeny základní informace o univerzální sběrnici PCI. Řekli jsme si také, že tato sběrnice existuje v několika variantách, které se od sebe odlišují především v napětí adresových, datových i logických signálů, v rychlosti sběrnice (přesněji řečeno frekvencí hodinového signálu) a také v šířce datové části sběrnice. Úroveň logických signálů (tj. napětí logické jedničky – logická nula se od tohoto napětí odvozuje) může nabývat hodnoty buď 5 voltů nebo 3,3 voltů. Taktovací frekvence a šířka datové sběrnice přímo určují maximální datový tok. Teoretické maximální přenosové rychlosti jsou vypsány v následující tabulce, přičemž platí, že reálné maximální rychlosti bývají o cca 10% až 20% nižší z důvodu latence při zpracování přerušení, většinou omezené velikosti dat přenášených v jednom bloku atd. U běžných desktopových počítačů se nejčastěji můžeme setkat se sběrnicí taktovanou na 33 MHz s šířkou datové části 32 bitů (teoretická maximální rychlost je tedy 132 MB.s-1) a úrovněmi logických signálů 5 voltů.

| Taktovací frekvence | Šířka datové části | Maximální datový tok |

|---|---|---|

| 33 MHz | 32 bitů | 132 MB.s-1 |

| 33 MHz | 64 bitů | 264 MB.s-1 |

| 66 MHz | 32 bitů | 264 MB.s-1 |

| 66 MHz | 64 bitů | 532 MB.s-1 |

| 133 MHz | 32 bitů | 532 MB.s-1 |

| 133 MHz | 64 bitů | 1066 MB.s-1 |

2. Tvary konektorů PCI sběrnic

Při návrhu konektorů sběrnice PCI museli její tvůrci vyřešit jeden poměrně závažný problém – jak zajistit, aby se do konektoru, na nějž jsou přiváděny pětivoltové signály, zasunovaly pouze karty určené pro 5 V a naopak. Po připojení karty určené pro rozhraní 3,3 voltů by mohlo dojít jak ke zničení samotné karty, tak i k poškození řadiče sběrnice či dalších připojených karet. Řešení je jednoduché – v konektoru jsou na přesně určených místech takzvané klíče. V podstatě se jedná o přerušení vlastního konektoru takovým způsobem, že v kartě musí být na příslušném místě vyříznut „zub“, jinak nedojde k jejímu zasunutí. Vzhledem k tomu, že existují sběrnice PCI s šířkou datové části 32 bitů a 64 bitů a současně (nezávisle na bitové šířce) se může jednat o rozhraní pracující na pěti voltech či 3,3 voltech, můžeme se v praxi setkat se čtyřmi typy konektorů. Na prvním obrázku jsou v dolní části zobrazeny konektory pro 32 bitovou PCI sběrnici, nahoře jsou možné tvary karet pro jednotlivé konektory.

Obrázek 1: Dva možné tvary konektorů pro třicetidvoubitovou PCI sběrnici

Všimněte si, že se klíče nachází jak na pětivoltové variantě, tak i na variantě s rozhraním 3,3 V, pokaždé však na jiném místě. Tímto způsobem je zaručeno, že do konektoru bude vždy vložena pouze karta určená pro dané rozhraní. Pokud se výrobce karty rozhodne vytvořit takzvanou univerzální kartu pracující jak na 3,3 V, tak i na 5 V, může takovou kartu jednoduše vyrobit – postačuje na plošném spoji udělat „zuby“ dva (teoreticky by bylo možné vytvořit i univerźální konektor, který by žádné klíče neobsahoval, z praktického hlediska však toto řešení postrádá smysl). Podobným způsobem je vyřešený konektor určený pro šedesátičtyřbitovou variantu sběrnice PCI. Samotný konektor je podobný, jako u PCI sběrnice s poloviční datovou šířkou (shodné je i umístění klíčů), ovšem na pravé straně se nachází další signály, které datovou šířku rozšiřují na požadovaných 64 bitů. Jak konektory, tak i možné tvary karet pro šedesátičtyřbitovou PCI jsou zobrazeny na druhém obrázku.

Obrázek 2: Dva možné tvary konektorů pro šedesátičtyřbitovou PCI sběrnici

K tvarům konektorů i plošných spojů desek, které se do konektorů zasouvají, je nutné říci ještě jednu důležitou informaci – šedesátičtyřbitové rozšíření je považováno za nepovinné (základní konektor má 62 pinů, rozšířený pak 94 pinů). Podobně jako u PC a ISA sběrnice, které byly postaveny na společném základě, je možné i do šedesátičtyřbitové varianty PCI zapojovat třicetidvoubitové karty. Mechanicky je to umožněno tím, že se za vlastní konektorovou částí plošného spoje karty již nenachází žádné součástky ani jiné prvky, které by zabraňovaly vložení karty do delšího konektoru – viz třetí obrázek, na kterém je zvuková karta zapojitelná do třicetidvoubitové i šedesátičtyřbitové varianty PCI nezávisle na tom, zda se jedná o rozhraní 3,3 voltů či pět voltů:

Obrázek 3: Zvuková karta určená pro sběrnici PCI

Požadavky na rozhraní PCI sběrnice se liší podle její verze. PCI verze 2.2 například pro systémy s frekvencí hodinových pulsů 66 MHz vyžaduje rozhraní 3,3 V, zatímco pro frekvenci 33 MHz je možná volba 3,3 V či 5 V. Ovšem na obou typech konektorů je vyžadována přítomnost napájecího napětí 3,3 V. U PCI verze 2.3 se již pracuje pouze s kartami s napětím 3,3 V či univerzálními kartami, pětivoltové karty již nejsou podporovány. PCI verze 3.0, což je finální standard, již s rozhraním 5 voltů nepočítá vůbec. To je vzhledem k technologickému vývoji pochopitelné.

Obrázek 4: Povolené kombinace karet a konektorů pro třicetidvoubitovou PCI

Obrázek 5: Povolené kombinace karet a konektorů pro šedesátičtyřbitovou PCI

3. Komunikace procesoru a zařízení připojených na PCI sběrnici

V normě PCI sběrnice je do všech podrobností popsán protokol přenosu dat i časový průběh všech důležitých signálů. Dodržení standardu je implementačně velmi složité, z tohoto důvodu je jednodušší použít na přídavné kartě již vytvořený a důkladně otestovaný zákaznický obvod, který zajistí veškerou potřebnou komunikaci zařízení s PCI sběrnicí. Mezi tento typ obvodů patří i čip S5933 nebo S5935 firmy AMCC (plným názvem „Applied Micro Circuits Corporation“), pomocí kterého je možné přenášet data přes sběrnici PCI několika způsoby, které se liší jak náročností implementace, tak i maximální dosažitelnou rychlostí a úrovní zatížení sběrnice. Mezi možnosti přesunu dat pomocí čipu S5933/S5935 patří:

- Jednosměrný přenos jednotlivých bytů, šestnáctibitových slov či 32bitových slov přes specializované registry, takzvané mailboxy. Pro omezení aktivního čekání na data lze využít možnosti generování přerušení při zápisu a/nebo čtení z mailboxu.

- Přímé čtení či zápis do paměti umístěné na připojené desce pomocí paměťových mapovaných regionů. Jedná se o takzvané Pass Thru operace. Pro tento typ komunikace musí být na přídavné desce vytvořena adresová a datová sběrnice, ke které je paměť připojena.

- Blokový přenos dat přes dvě jednosměrné fronty typu FIFO. Jednou z modifikací tohoto způsobu přenosu je i několikrát zmíněný bus-master přenos, který se provádí v případě, že řízení přenosu převezme přídavná karta připojená na PCI sběrnici. Celý přenos může řídit právě čip AMCC 5933/5935, který obstará čtení z paměti přídavné karty a zápis do operační paměti hostitelského počítače, popř. i opačnou operaci.

Obrázek 6: Karta určená pro šedesátičtyřbitovou PCI sběrnici s rozhraním 3,3 V

V dalším textu se budu zmiňovat o některých registrech, přičemž se rozlišují tři skupiny registrů:

- PCI configuration registers – jejich hodnoty bývají typicky uloženy v nevolatilní paměti na přídavné kartě, je zde mj. i identifikace karty a identifikace výrobce. Přes čip AMCC jsou hodnoty těchto registrů přístupné pro čtení, čehož využívá například BIOS počítače při přidělování adresových oblastí pro jednotlivé přídavné karty.

- PCI bus operation registers – jedná se o skupinu šestnácti 32bitových registrů, které řídí činnost čipu AMCC, právě zde se nachází mailboxy, obousměrná komunikační fronta, řídicí registry pro bus master přenos atd. Tyto registry jsou dostupné pro čtení příp. zápis na straně PCI sběrnice.

- Add-on bus operation registers – registry přístupné pouze z přídavné karty, které řídí obvod AMCC „z druhé strany“. Typicky k těmto registrům přistupuje mikrořadič či DSP umístěný na přídavné desce. Například zápis do mailboxu OMB#1 procesorem počítače znamená, že se zapisovaný obsah na „druhé straně“ objeví v registru AIMB#1.

nvRAM firmware [AMCC] ...... PCI sběrnice ...... [North bridge] ...... [Procesor] karty

4. Přenos dat přes mailboxy čipu AMCC S5933/S5935

Přenos dat po PCI sběrnici přes mailboxy čipu AMCC S5933/S5935 je velmi jednoduchý, protože mailboxy se z programátorského hlediska chovají jako registry. Do každého mailboxu lze zapsat informaci (jeden byte, šestnáctibitové slovo či 32bitové slovo) a tuto informaci je možné z mailboxu následně přečíst. Komunikace však funguje jednosměrně – pokud se informace zapíše ze strany přídavné karty, je ji možné přečíst přes sběrnici PCI a naopak. Obvody AMCC S5933 a S5935 mají vytvořeny čtyři mailboxy pro přenos dat směrem do periferního zařízení a čtyři mailboxy pro přenos opačný, tj. z přídavné karty směrem k procesoru.

Výstupní mailboxy jsou v adresovém prostoru PCI zařízení pojmenovány OMB#1 až OMB#4 (Output MailBox), vstupní mailboxy mají jména IMB#1 až IMB#4 (Input MailBox). Zaplnění nebo naopak přečtení (vyprázdnění) mailboxu je signalizováno nastavením příslušného stavového bitu v registrech MBEF/AMBEF (MailBox Empty/Full status register), přičemž je možné generovat přerušení, pokud jsou korektně nastaveny řídicí registry INTCSR/AINT (Interrupt Control/Status register). Přerušení je však možné nastavit pouze pro jeden mailbox na každé komunikující straně, což však není omezující vlastnost sběrnice PCI, ale obvodu AMCC. V některých případech může být prospěšné, že se mohou automaticky prohazovat pořadí bytů ve slovech ukládaných do mailboxů.

Obrázek 7: Základní deska obsahující dvě varianty PCI sběrnice

Každé čtení z mailboxu ze strany PCI (tj. při komunikaci procesoru s čipem AMCC) vyžaduje minimálně tři hodinové cykly na sběrnici. V prvním cyklu se přenese adresa mailboxu (který leží v adresovém prostoru PCI zařízení), druhý cyklus je věnován dekódování adresy a přenosu přes čip AMCC a teprve ve třetím cyklu je možné data z mailboxu přečíst. Vzhledem k tomu, že jeden hodinový cyklus PCI sběrnice má na počítačích typu PC délku trvání 0,03 mikrosekundy, trvá čtení dat z mailboxu čipu AMCC S5933/S5935 cca 0,1 mikrosekundy – jde tedy o jednoduchý ale relativně pomalý způsob přenosu dat. Také se jedná o snadno „odladitelný“ přenos dat – na obou stranách čipu AMCC může vývoj a ladění probíhat zcela odděleně. Pokud se někdo ze čtenářů zabývá návrhem karet do PCI sběrnice, je toto nejlepší způsob, kde začít.

Zápis do mailboxu ze strany PCI sběrnice (tj. procesoru) je poněkud rychlejší, neboť je zapotřebí pouze dvou hodinových cyklů: v prvním cyklu je přenesena adresa mailboxu a ve druhém cyklu jsou přenesena potřebná data.

5. Přenosové operace typu Pass Thru (do paměti mapované regiony)

Dalším možným způsobem přenosu dat z/do operační paměti hostitelského počítače je použití paměťově mapovaných regionů. Jedná se o takzvané Pass Thru operace, při kterých se část paměťového prostoru přídavné karty mapuje do paměťového prostoru hostitelského počítače – pro procesor či jiné zařízení se tedy například framebuffer grafického akcelerátoru chová jako souvislá oblast operační paměti. Pro zajištění Pass Thru operací obsahuje čip AMCC několik registrů, kterými se nastavuje jak paměťový rozsah, tak i adresa, od které se bude mapování adres provádět.

Čtení nebo zápis z paměti na přídavné kartě je indikován signály na PCI sběrnici; konkrétně se jedná o signály resp. vodiče C/BE0# až C/BE3#, pomocí kterých procesor či jiné zařízení posílá kód operace, která se má provést na přídavné kartě. Pro čtení z paměti umístěné na kartě musí být procesorem poslán příkaz Memory Read, pro zápis pak příkaz Memory Write. Adresa, ze které se má číst, nebo na kterou se má zapisovat, se posílá po vodičích AD00 až AD31, tedy po běžných adresových a datových vodičích sběrnice PCI (jak jsem již zdůrazňoval dříve, je sběrnice PCI multiplexovaná, proto jsou adresové a datové vodiče totožné).

Pro každé zařízení připojené ke sběrnici PCI je pomocí takzvaných PCI konfiguračních registrů (jedná se o konfigurační registry BADR#0 až BADR#5) definováno maximálně šest paměťových regionů, které jsou pro dané periferní zařízení vyhrazeny a do nichž je možno zapisovat data, nebo data naopak číst. Každý region může pracovat ve dvou režimech – šestnáctibitovém a 32 bitovém. Šestnáctibitový region je určen pro práci v operačních systémech DOS a Windows 3.11, 32bitový region je použitelný ve všech 32bitových operačních systémech, včetně Linuxu a BSD Unixu.

Počáteční adresa regionu je přidělována v době inicializace počítače systémem BIOS, může se tedy s každým spuštěním lišit. Nicméně ovladač zařízení si kdykoli může přečíst všechny počáteční adresy i povolené rozsahy adres, které jsou uloženy v registrech BADR#0 – BADR#5 takže práce s mapovanou pamětí je poměrně jednoduchá a nijak se neliší od práce s regulární operační pamětí hostitelského počítače.

Při práci s čipem AMCC S5933/S5935 jsou do prvního paměťového regionu, jehož počáteční adresa a velikost je uložena v konfiguračním registru BADR#0, mapovány přímo řídicí a stavové registry čipu AMCC. Ostatní čtyři paměťové regiony, jejichž konfiguraci lze zjistit z registrů BADR#1 – BADR#4, mohou být nakonfigurovány v době inicializace systému přímo přídavnou kartou, která kvůli tomu musí obsahovat stálou (nevolatilní) paměť typu ROM, v níž je konfigurace uložena (pokud se tedy nejedná o nejmenované síťové karty od Intelu, které při vhodných podmínkách obsah své nevolatilní paměti ztratí…). Poslední region definovaný registrem BADR#5 není čipem AMCC podporován.

Každá paměťová oblast může mít velikost až 512MB, což je pro přenos prakticky všech myslitelných typů dat zcela dostatečná hodnota. Při zápisu či čtení přes paměťový region dochází k zápisu adresy do registru APTA a dat do registru APTD (registry APTA a APTD jsou umístěny na čipu AMCC S5933/S5935. Tyto registry je možné na straně přídavné karty číst a samozřejmě do nich zapisovat nové hodnoty.

Pass Thru operace přístupu do paměti pracují na principu handshakingu. Pokud se zapisují data směrem z PCI sběrnice (tj. buď procesorem nebo jiným zařízením), musí přídavná karta tato data přečíst, jinak nedojde k uvolnění PCI sběrnice. Pokud naopak procesor či jiné zařízení čte data z paměti přídavné karty, musí ovládací obvod karty data přes AMCC čip skutečně zapsat, jinak se opět PCI sběrnice neuvolní. To znamená, že pokud se z nějakého důvodu špatně vyhodnotí objem přenášených dat, dochází zákonitě k zastavení celého systému, neboť procesor buď na nějaká data marně čeká, nebo naopak přídavná karta čeká se zápisem dat, které procesor už nepřečte – v obou případech dochází k nepotvrzení operace čtení/zápisu. Z hlediska stability celého systému je nutno tuto vlastnost považovat za značnou nevýhodu – z vlastní zkušenosti také mohu potvrdit, že všechny chyby jsou kvůli okamžitému „zamrznutí“ počítače těžko odhalitelné, zejména v případě, že není k dispozici logický analyzátor PCI (to je pěkná, ale také dosti drahá hračka).

Další důležitou vlastností Pass Thru operací je rychlost přenosu dat. Čip AMCC S5933/S5935 v tomto režimu pracuje na plné rychlosti PCI sběrnice, v každém cyklu tedy lze (kvůli multiplexování adres a dat) přečíst či zapsat buď adresu či jeden balík informace – 32 bitů.

Pokud je použit burst režim přenosu, kdy se adresa přenáší pouze na začátku sekvence dat, je teoreticky možné dosáhnout maximální přenosové rychlosti sběrnice PCI, tj. 132 MB.s-1. Z tohoto hlediska jsou tedy paměťové přenosy pomocí Pass Thru operací stejně výkonné jako bus-master režim přenosu.

6. Blokové přenosy dat

Z hlediska maximálního objemu přenesených dat za určitou časovou jednotku je nejvýhodnější provádět blokový přenos dat po PCI sběrnici s využitím burst režimu. Ten je možné implementovat dvěma způsoby:

- Celé řízení přenosu převezme procesor počítače, který pomocí řadiče PCI sběrnice nastaví komunikační protokol, počáteční adresu přenosu dat a počet přenesených slov. Poté se v programové smyčce provede vlastní přenos, tj. generování příkazů Memory Read na PCI sběrnici a čtení dat.

- Řízení přenosu převezme přímo PCI zařízení, které se tak, podle terminologie PCI, pro tento přenos stane Mastrem. Zařízení typu Master má odpovědnost za veškeré ustanovení komunikačního protokolu i za jeho provedení, včetně generování potřebných signálů na sběrnici PCI.

7. Bus-master přenos

V následujících odstavcích se budu zabývat pouze druhým případem, který budu nazývat (opět v rámci terminologie PCI) bus-master přenos. Pro bus-master přenos je obvod AMCC S5933/S5935 vybaven několika registry. Z těchto registrů je nejdůležitější registr FIFO, pomocí kterého se zapisuje či čte z jedné jednostranné fronty. Pro čtení dat z PCI zařízení je použita první fronta, pro zápis dat na PCI zařízení se používá fronta druhá. Při čtení nebo zápisu do fronty může docházet ke konverzi dat mezi různými typy uložení bitů a bytů v přenášených slovech.

Další registry jsou MWAR (Master Write Address Register) a MRAR (Master Read Address Register), ve kterých jsou uloženy počáteční adresy paměťových regionů v operační paměti počítače, na které se budou zapisovat popř. ze kterých se budou číst data pomocí bus-master přenosu. Před vlastním přenosem se počet zapisovaných slov uloží do registru MWTC (Master Write Transfer Count Register.). V případě čtení dat se jejich počet zapíše do registru MRTC (Master Read Transfer Count Register.). Pokud je komunikace mezi počítačem a PCI zařízením korektní, začne přenos probíhat při zápisu nenulové hodnoty do jednoho z registrů MWTC či MRTC. Obsah registrů MWAR, MRAR, MWTC a MRTC se během přenosu průběžně mění, fungují tedy jako počitadla, čehož je možné využít například při ladění.

Na konci provádění blokového bus-master přenosu může být generováno přerušení, pomocí nějž je procesoru oznámeno uvolnění PCI sběrnice. Pokud je generování přerušení zakázáno, musí procesor průběžně testovat stav registrů MWTC nebo MRTC, jejichž hodnota se během přenosu snižuje směrem k nule (samozřejmě se většinou nejedná o zcela aktivní a neustálé čtení registrů v programové smyčce, na úrovni API jádra jsou k dispozici funkce, které dokážou během čekání předat řízení dalšímu procesu). Generování přerušení lze nastavit jak pro blokové operace čtení, tak i pro blokový zápis v registru INTCSR (Interrupt Control/Status Register), který je taktéž umístěn na čipu AMCC S5933/S5935. Režim přenosu lze změnit zápisem korektních informací do registru MCSR (Master Control/Status Register), ve kterém lze mimo jiné i předepsat prioritu čtení před zápisem, či naopak zápisu před čtením.

Každá fronta má délku osmi 32bitových slov. Při vyprázdnění fronty či při jejím přeplnění je generováno přerušení na straně PCI sběrnice či přídavné karty, na jejíž podnět musí být do fronty zapsána či přečtena další data. Pomocí registru MCSR však může být nastaven režim, kdy je přerušení generováno už při překročení poloviční kapacity fronty (tj. čtvrtého slova). Vzhledem k tomu, že je v tomto případě přerušení generováno dříve, může přenos probíhat dále současně s plněním fronty – tímto způsobem je možné zabezpečit kontinuální burst přenos celého bloku dat, čímž dochází k optimálnímu využití přenosového pásma PCI sběrnice, jelikož při burst přenosu se nemusí neustále přenášet adresy paměťových míst.

Jedinou vážnější nevýhodou tohoto způsobu přenosu dat, je nutnost přenesení celých násobků 32bitových slov. Nelze tedy přenést například lichý počet bytů – první či poslední byty celé sekvence by se musely přes registr FIFO přenést programově. Většinou lze toto omezení obejít buď na straně programu nebo firmwaru na přídavné desce. Bus-master přenos se implementuje a ladí poměrně snadno – podle mých zkušeností je nejlepší nejprve vlastní kartu „naučit“ komunikovat přes mailboxy a když vše pracuje dobře, urychlit blokové přesuny dat pomocí bus-master přenosu.

8. Literatura a odkazy na Internetu

- Wikipedia EN: Peripheral Component Interconnect,

http://en.wikipedia.org/wiki/Peripheral_Component_Interconnect - PCI Vendor and Device Lists,

http://www.pcidatabase.com/index.php - Seznam PCI VID/DID,

http://www.pcidatabase.com/reports.php?type=csv - PCI bus pinout,

http://pinouts.ru/Slots/PCI_pinout.shtml - How to recognise a 3.3 Volt PCI slot,

http://www94.web.cern.ch/hsi/s-link/devices/s32pci64/slottypes.html - Computer Bus and BackPlane Design,

http://www.interfacebus.com/Design_Interface_table.html - VESA Local Bus,

http://en.wikipedia.org/wiki/VESA_Local_Bus - VESA Local Bus,

http://cs.wikipedia.org/wiki/VESA_Local_Bus - Applied Micro Circuits Corporation:

S5935 PCI product Data Book,

Applied Micro Circuits Corporation, San Diego, 1999 - Bhatt Ajay V.:

Creating a PCI Express Interconnect,

Technology and Research Labs, Intel Corporation, 2003 - Intel Coproration, Neshati Ramin:

PCI Express Base Specification 1.0a,

Intel Corporation, 2003

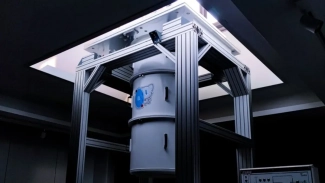

Obrázek 8: Analyzátor PCI sběrnice, který se zapojuje mezi základní desku a PCI kartu

9. Obsah následující části seriálu

Prakticky nejznámějším rozšířením sběrnice PCI je sběrnice označovaná PCI Express. Nejedná se však o faktické rozšíření na fyzické úrovni, ale na úrovni programové. Na fyzické úrovni se jedná o zcela nový (a nutno říci, že velmi zajímavě navržený) typ sběrnice, která se v některých aspektech dokonce podobá propojovací síti s topologií odlišnou od topologie sběrnicové (lineární). Přenosová rychlost se u této sběrnice pohybuje v řádech jednotek až desítek GBs-1, pro dnes nejčastější měděné spoje je maximální rychlost stanovena na 10 GBps-1. Právě tímto typem sběrnice se budeme podrobněji zabývat v navazující části tohoto seriálu. Popíšeme si také port AGP, včetně jeho zvláštních režimů a funkcí.